# **TOSHIBA**

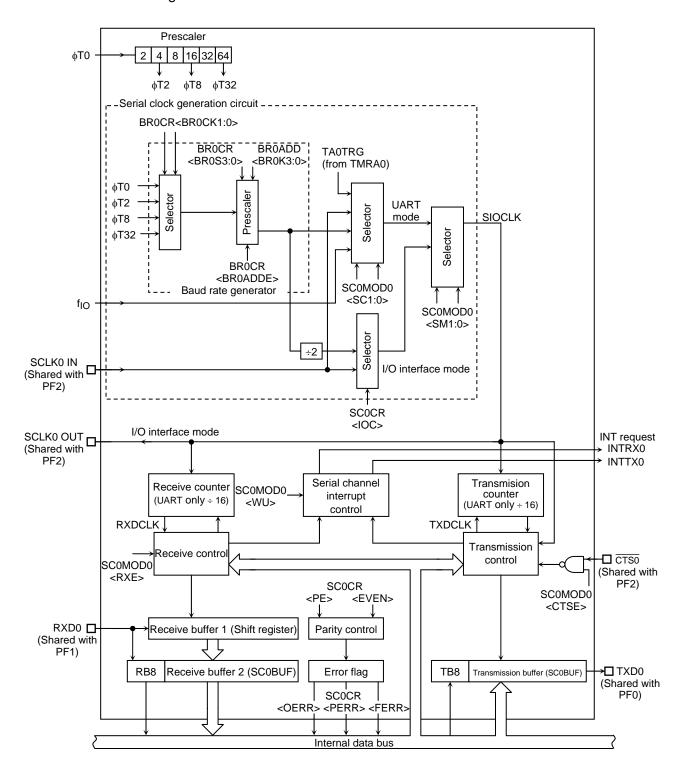

**TOSHIBA Original CMOS 16-Bit Microcontroller**

# TLCS-900/H1 Series

TMP92C820FG

# **TOSHIBA CORPORATION**

Semiconductor Company

## **Preface**

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

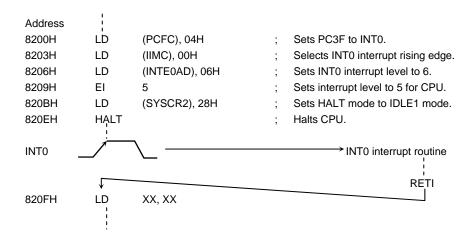

# \*\*CAUTION\*\* How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts = (INT0 to INT3, INTKEY, INTRTC, INTALM0 to INTALM4), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of f<sub>FPH</sub>) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

#### CMOS 32-bit Microcontrollers

## TMP92C820FG/JTMP92C820

#### Outline and Device Characteristics

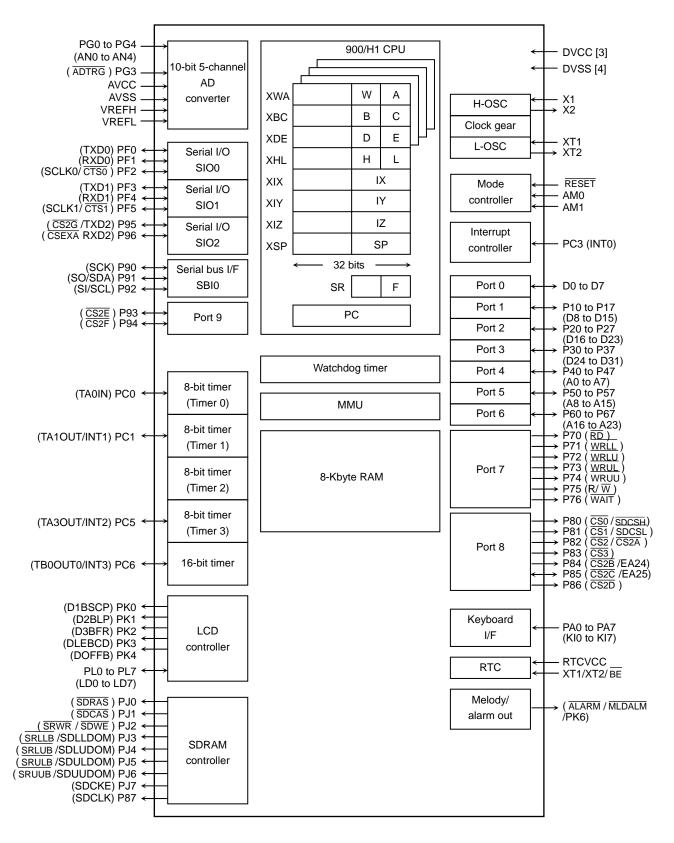

TMP92C820 is high-speed advanced 32-bit microcontroller developed for controlling equipment which processes mass data.

TMP92C820 is a microcontroller which has a high-performance CPU (900/H1 CPU) and various built-in I/Os. TMP92C820FG is housed in a 144-pin flat package. JTMP92C820 is a 144-pad chip product.

Device characteristics are as follows:

#### (1) CPU: 32-bit CPU (900/H1 CPU)

- Compatible with TLCS-900, 900/L, 900/L1, 900/H's instruction code

- 16 Mbytes of linear address space

- General-purpose register and register banks

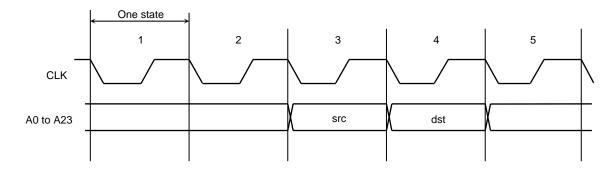

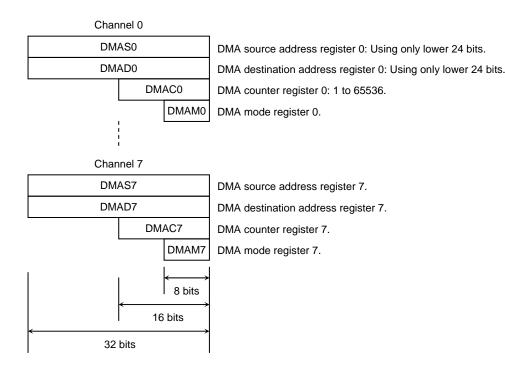

- Micro DMA: 8 channels (250 ns/4 bytes at fsys = 20 MHz, best case)

- (2) Minimum instruction execution time: 50 ns (at sys = 20 MHz)

#### **RESTRICTIONS ON PRODUCT USE**

070208FBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as

- set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties. 021023\_C

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

**TOSHIBA**

- (3) Internal memory

- Internal RAM: 8 Kbytes (can use for code section)

- Internal ROM: None

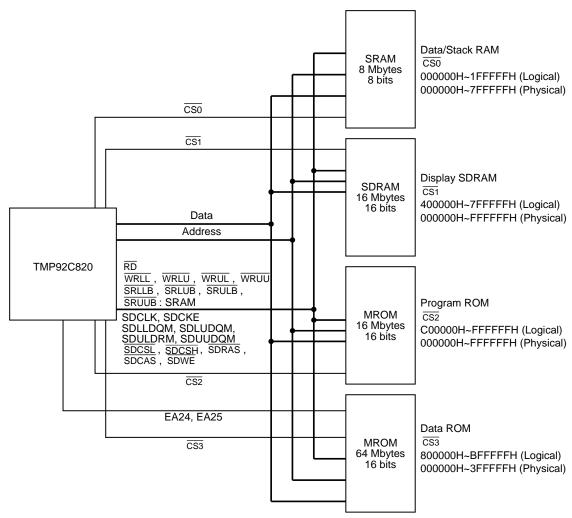

- (4) External memory expansion

- Expandable up to 136 Mbytes (Shared with program/data area)

- Can simultaneously support 8-/16-/32-bit width external data bus .... Dynamic data bus sizing

- Separate bus system

- (5) Memory controller

- Chip select outputs: 4 channels

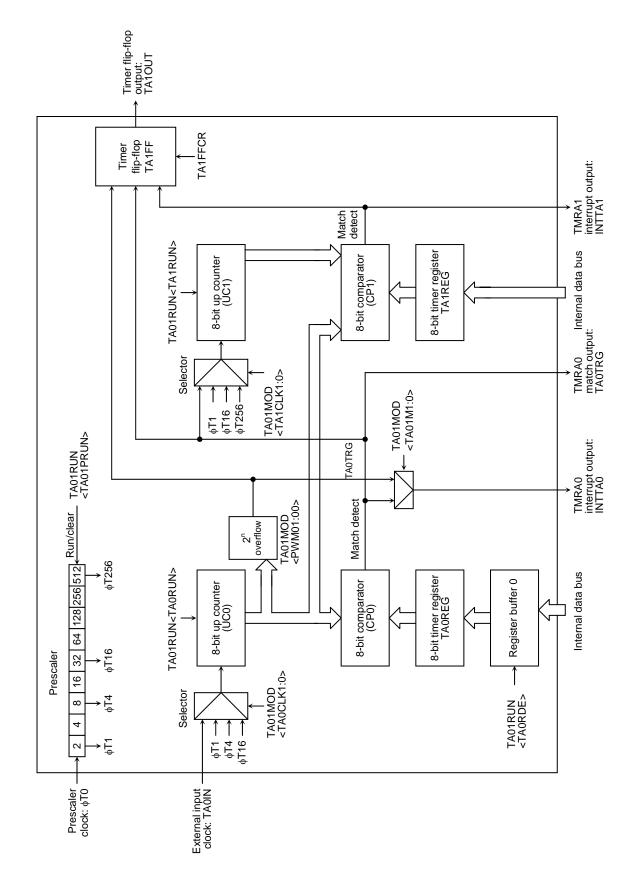

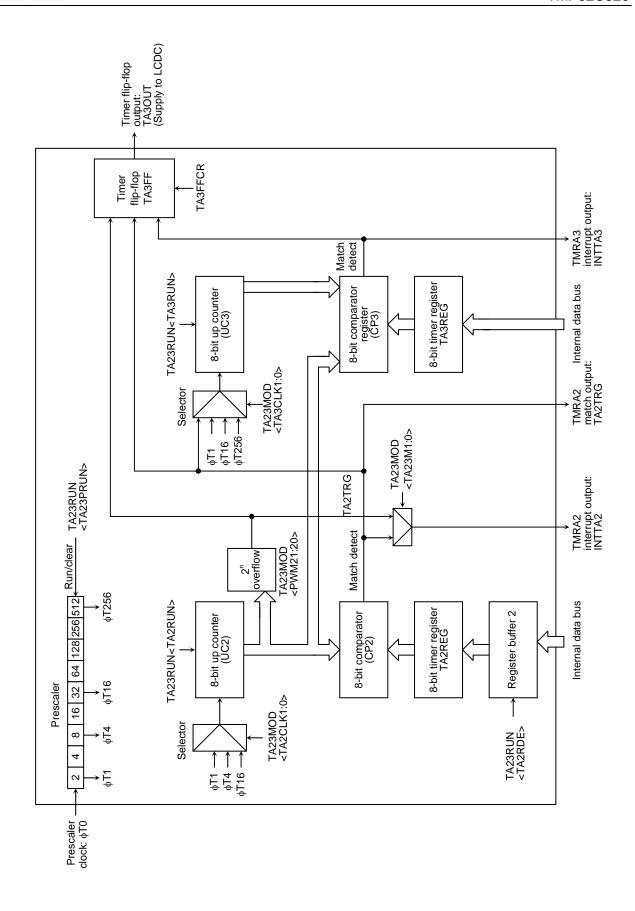

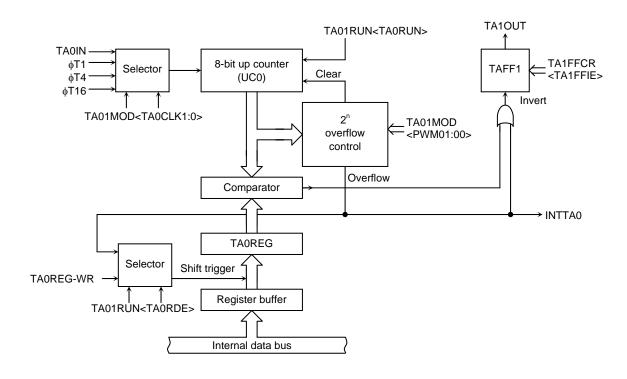

- (6) 8-bit timers: 4 channels

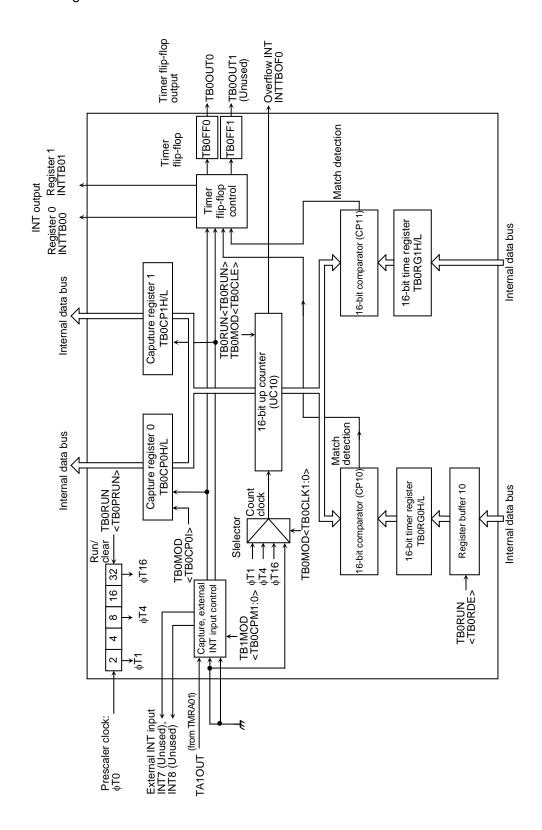

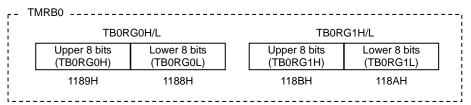

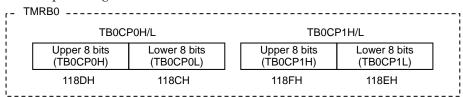

- (7) 16-bit timer/event counter: 1 channel

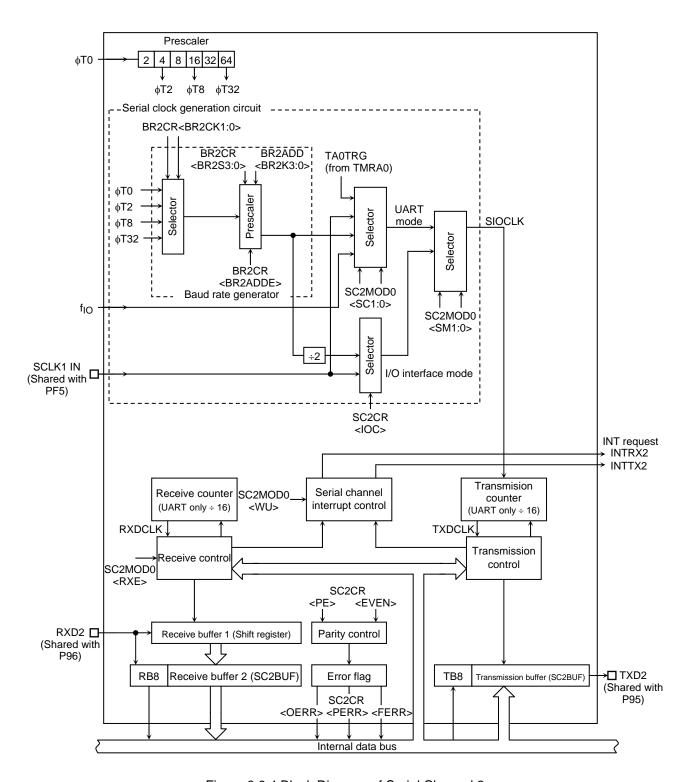

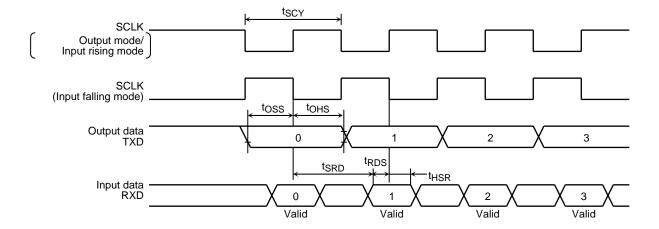

- (8) General-purpose serial interface: 3 channels

- UART/synchronous mode

- IrDA

- (9) Serial bus interface: 1 channel

- I<sup>2</sup>C bus mode

- Clock synchronous select mode

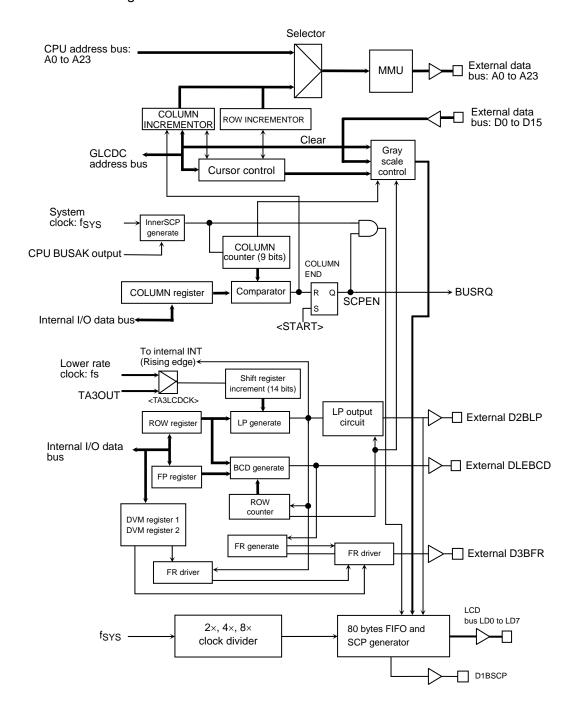

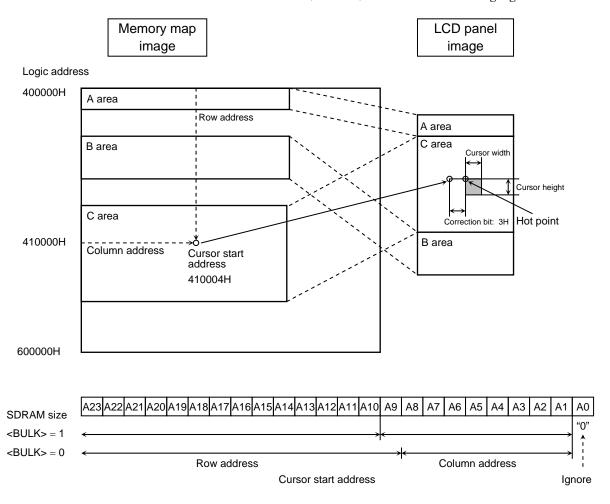

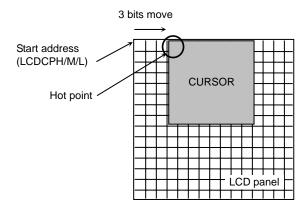

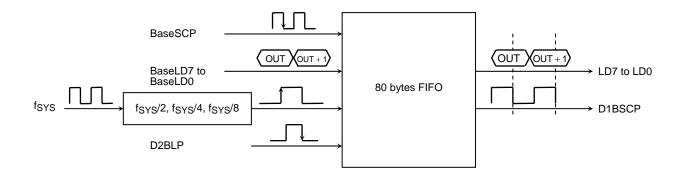

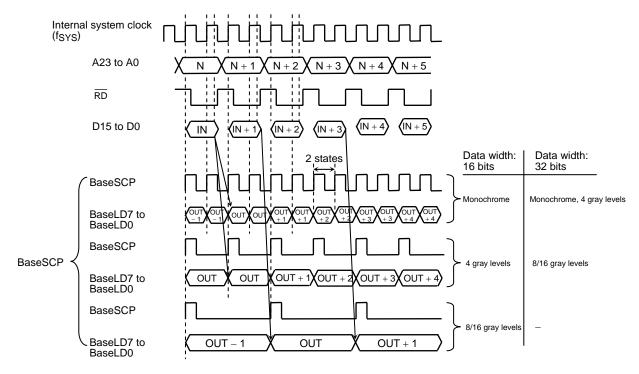

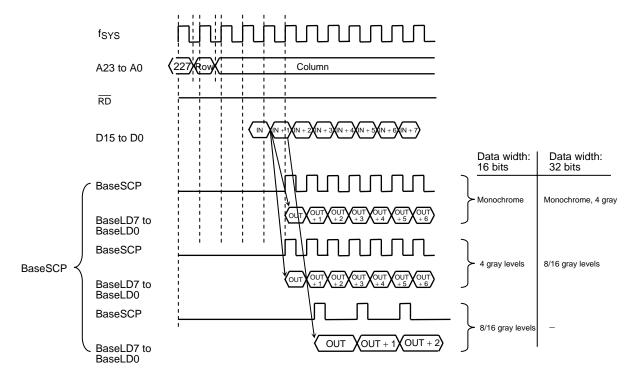

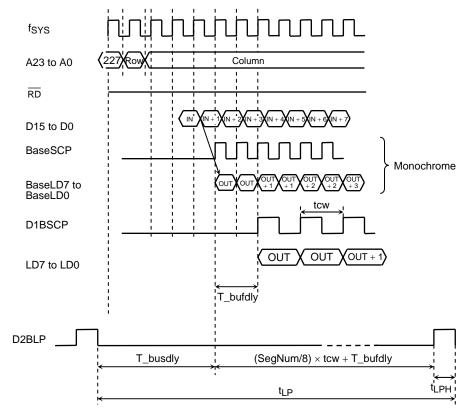

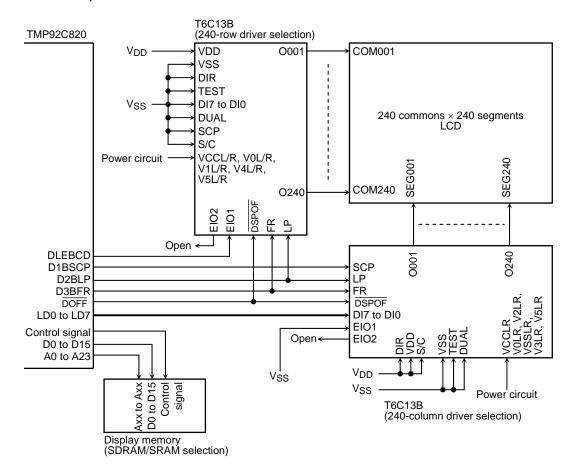

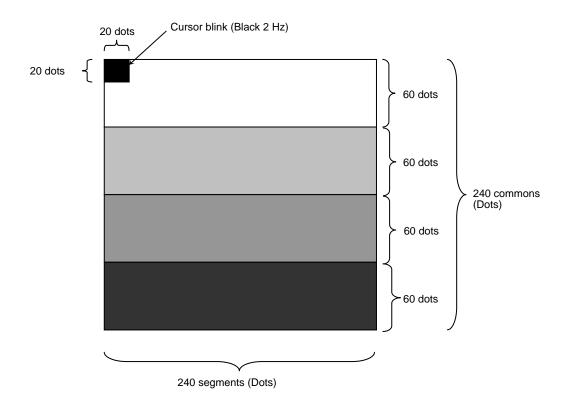

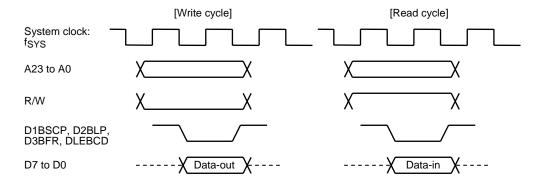

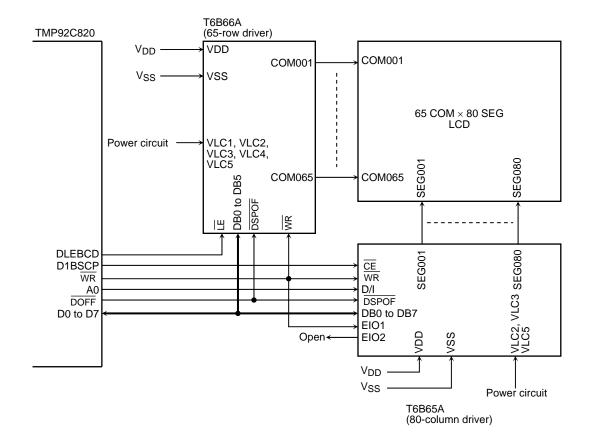

#### (10) LCD controller

- Shift register/built-in RAM LCD driver

- Supported 16, 8 and 4 gray-levels and black and white

- Hardware blinking cursor

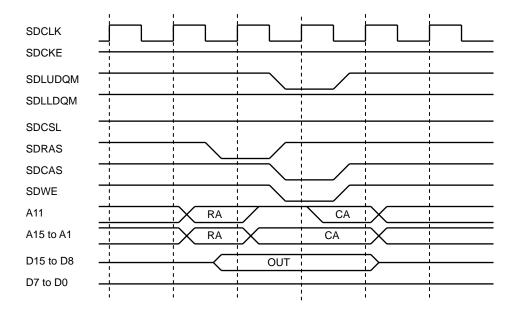

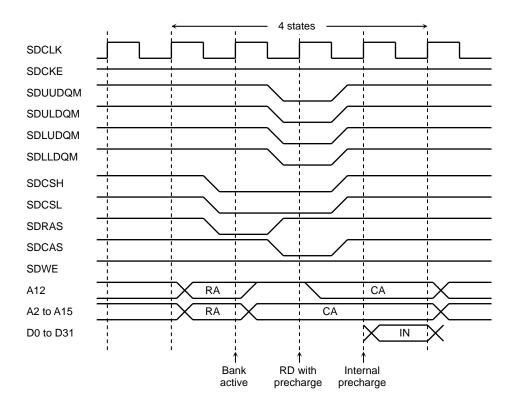

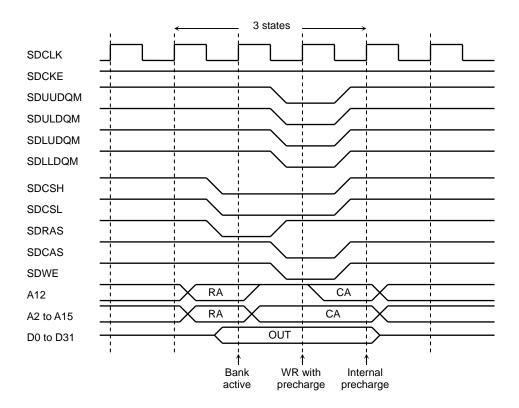

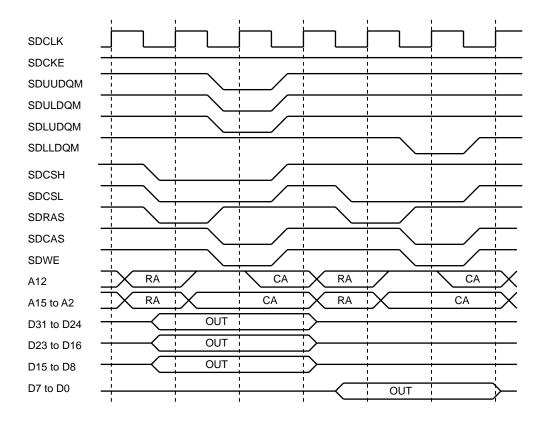

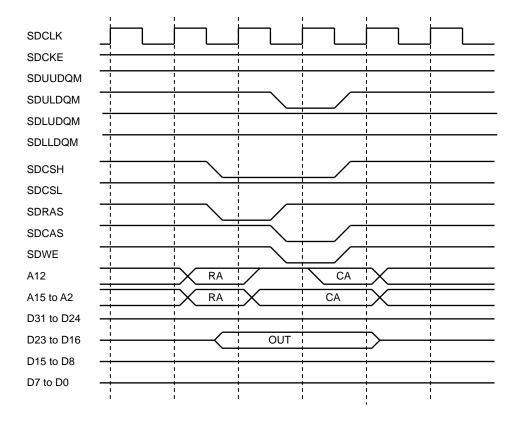

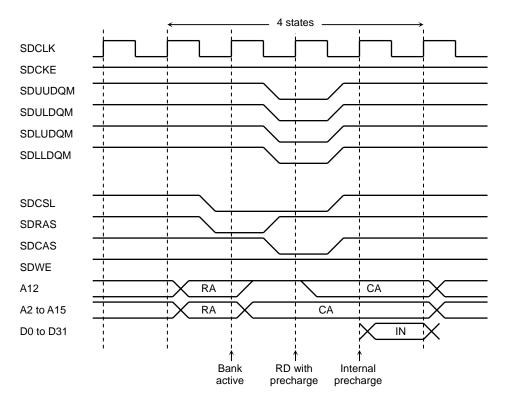

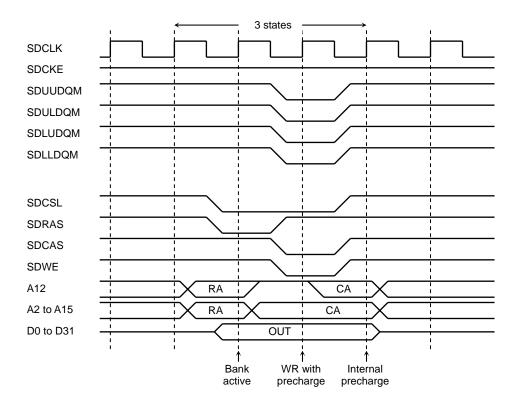

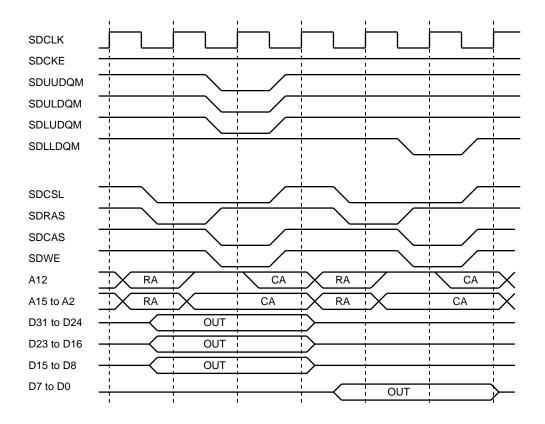

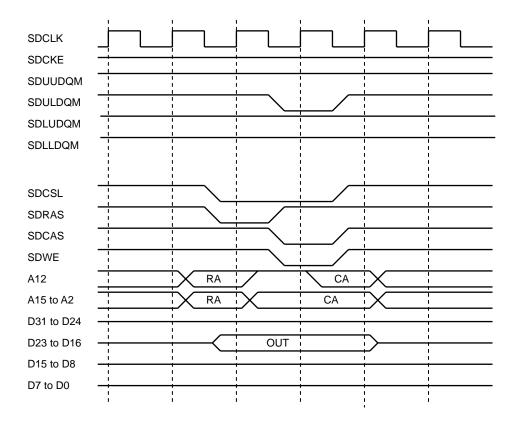

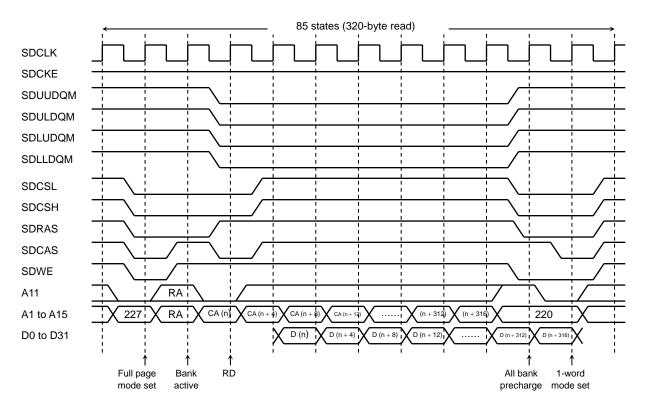

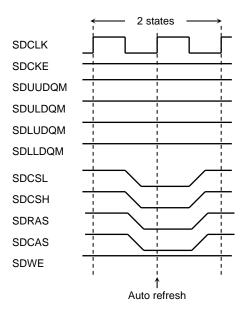

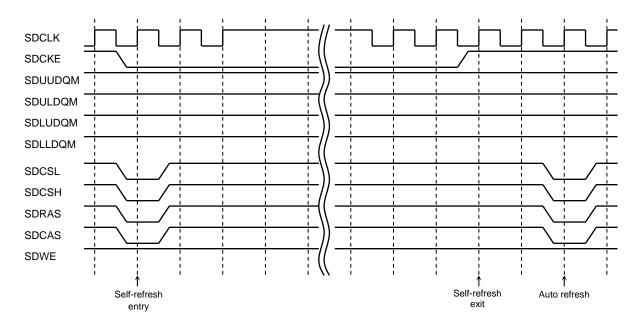

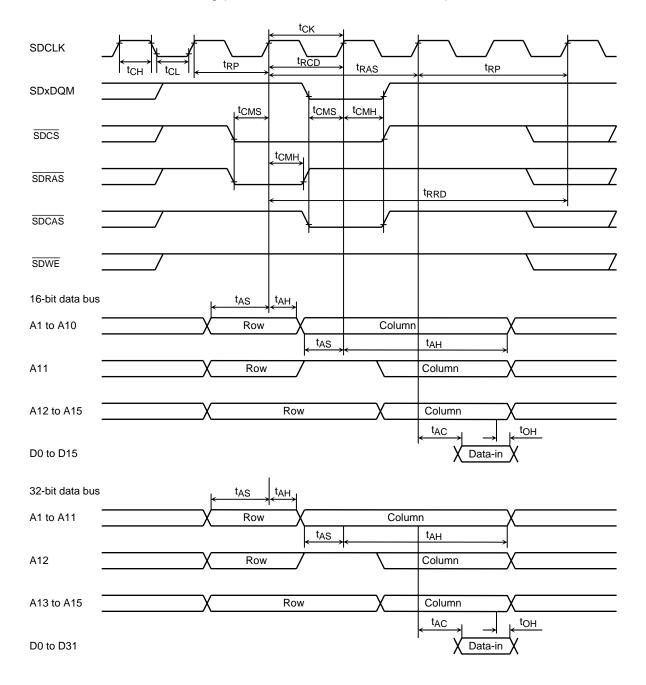

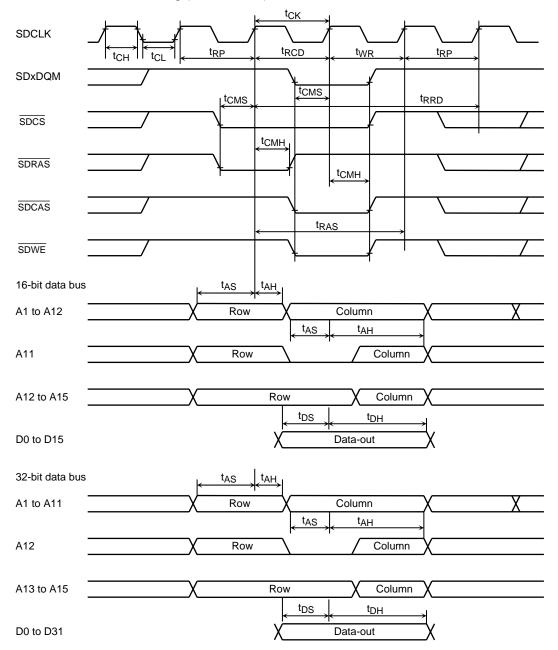

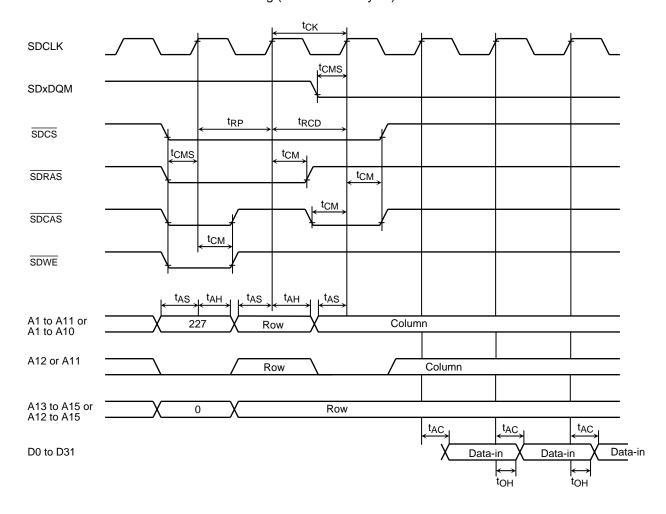

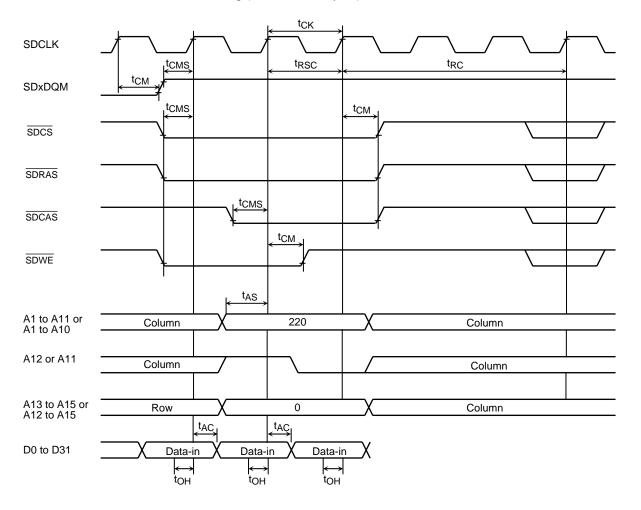

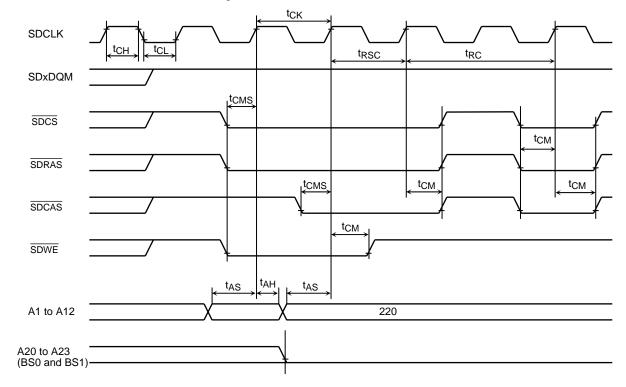

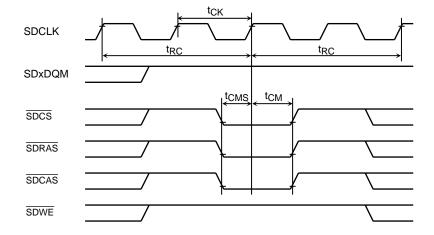

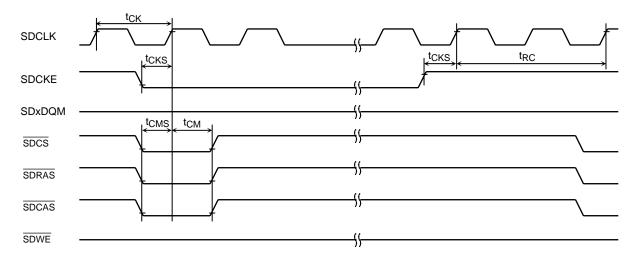

- (11) SDRAM controller

- Supported 16-M, 64-M and 128-Mbit SDRAM with 16-/32-bit data bus

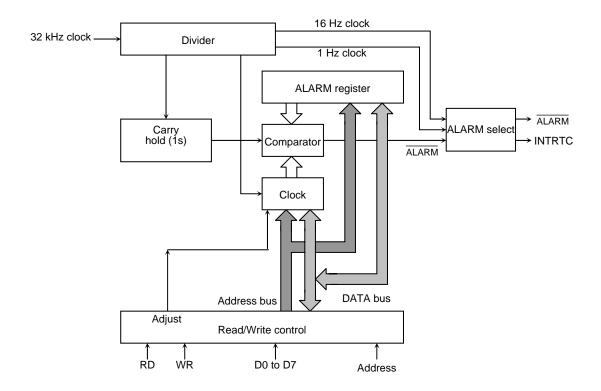

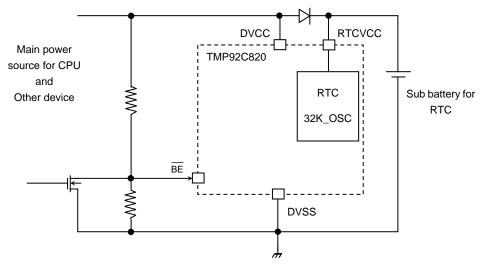

- (12) Timer for real-time clock (RTC)

- Based on TC8521A

- Separate the power supply

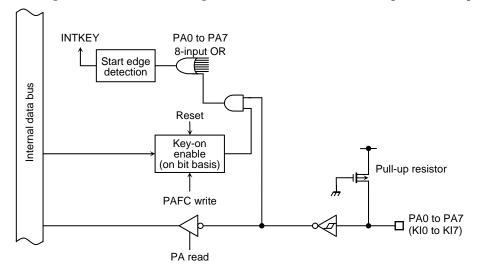

- (13) Key-on wakeup (Interrupt key input)

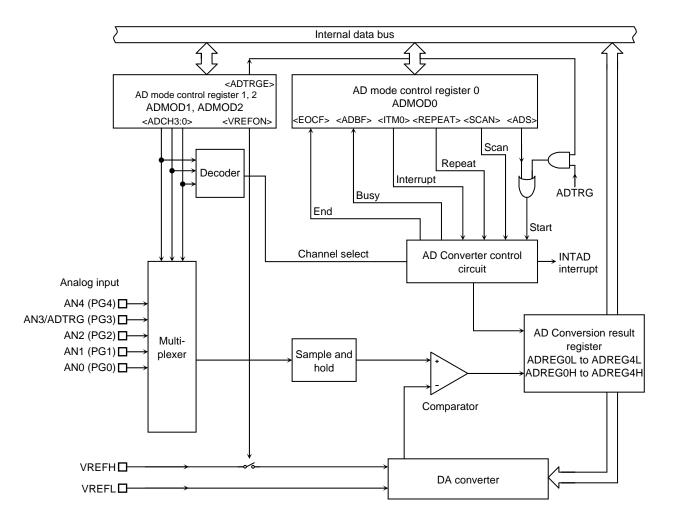

- (14) 10-bit AD converter: 5 channels

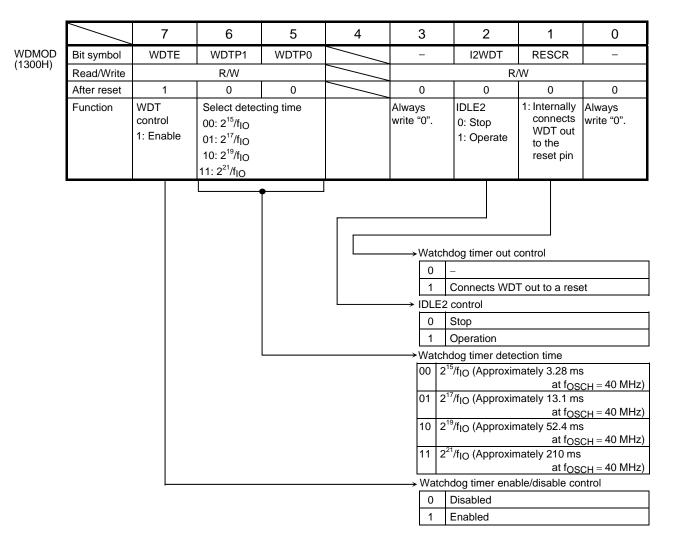

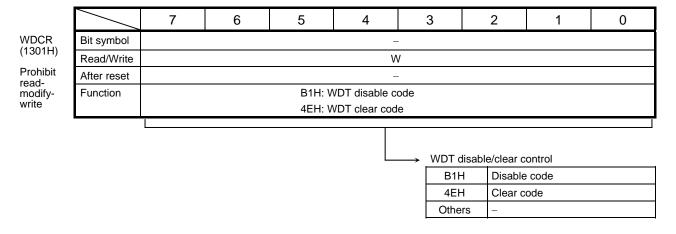

- (15) Watchdog timer

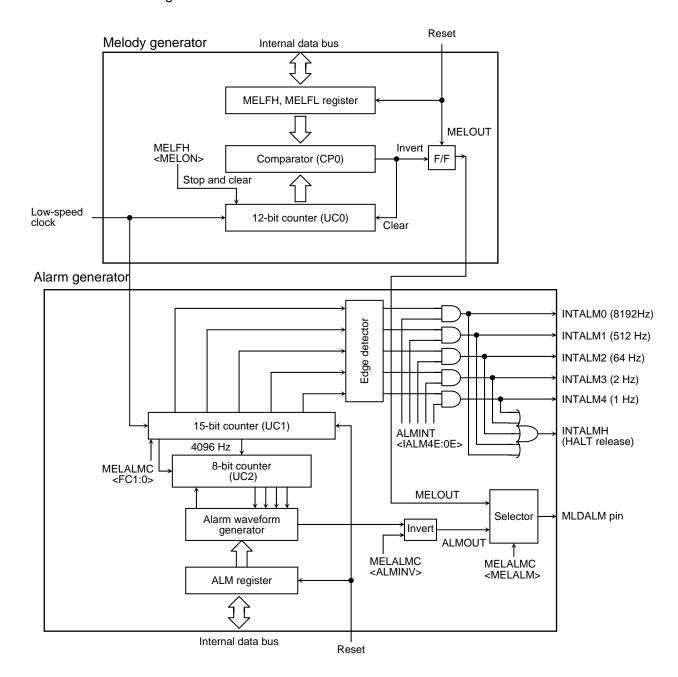

- (16) Melody/alarm generator

- Melody: Output of clock 4 to 5461 Hz

- Alarm: Output of the 8 kinds of alarm pattern

- Output of the 5 kinds of interval interrupt

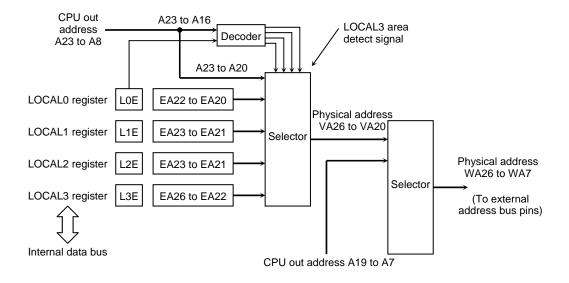

#### (17) MMU

• Expandable up to 136 Mbytes (4 local areas/8 bank methods)

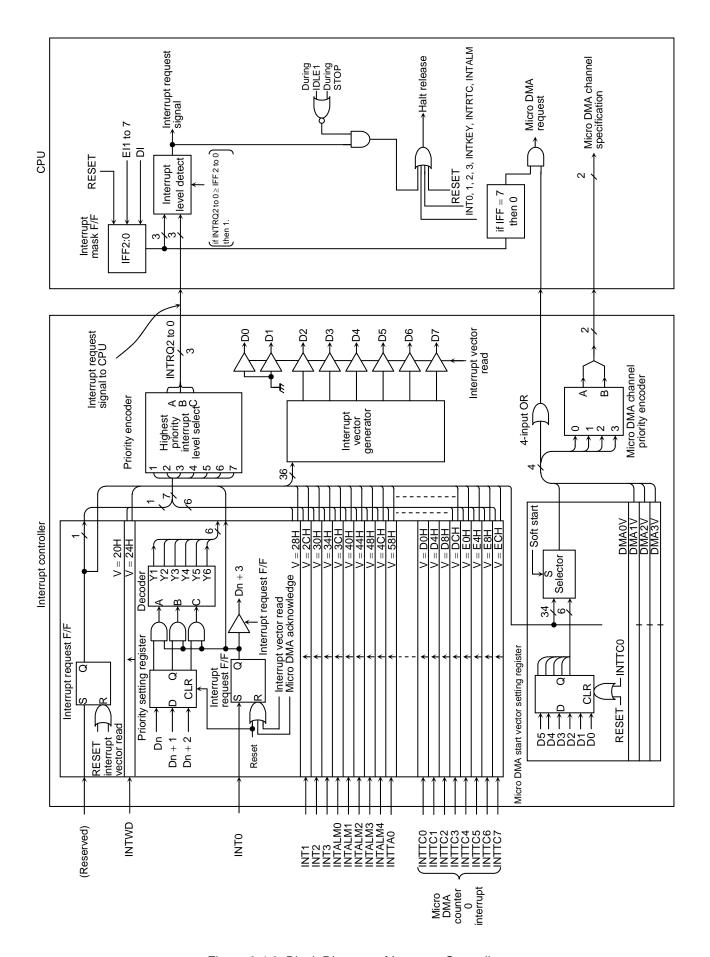

#### (18) Interrupts: 45 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 31 internal interrupts: Seven selectable priority levels

- 5 external interrupts: Seven selectable priority levels (4-edge selectable)

92C820-2 2007-02-16

(19) Input/output ports: 83 pins (Except Data bus (16bit), Address bus (24bit) and RD pin)

#### (20) Standby function

• Three HALT modes: IDLE2 (Programmable), IDLE1, STOP

## (21) Triple-clock controller

- Clock gear function: Select a high-frequency clock fc to fc/16

- RTC (fs = 32.768 kHz)

#### (22) Operating voltage

- DVCC = 3.0 to 3.6 V

- RTCVCC = 2.0 to 3.6 V

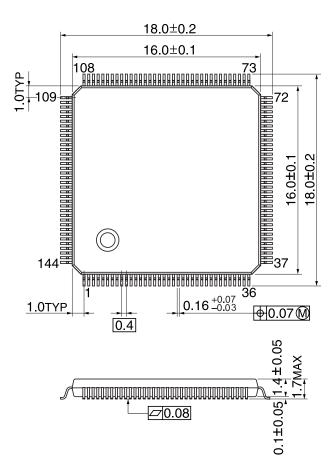

#### (23) Package

- 144-pin QFP (P-LQFP144-1616-0.40C)

- Chip form supply also available. For details, contact your local Toshiba sales representative

92C820-3 2007-02-16

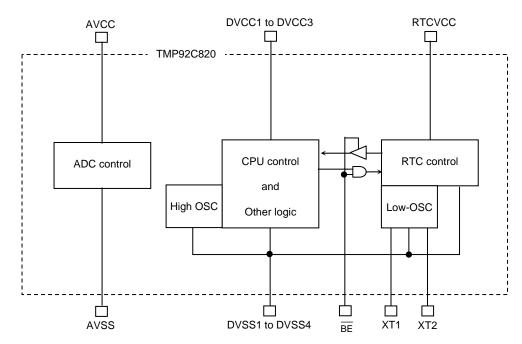

Figure 1.1 TMP92C820 Block Diagram

# 2. Pin Assignment and Functions

The assignment of input/output pins for the TMP92C820, their names and functions are as follows:

#### 2.1 Pin Assignment

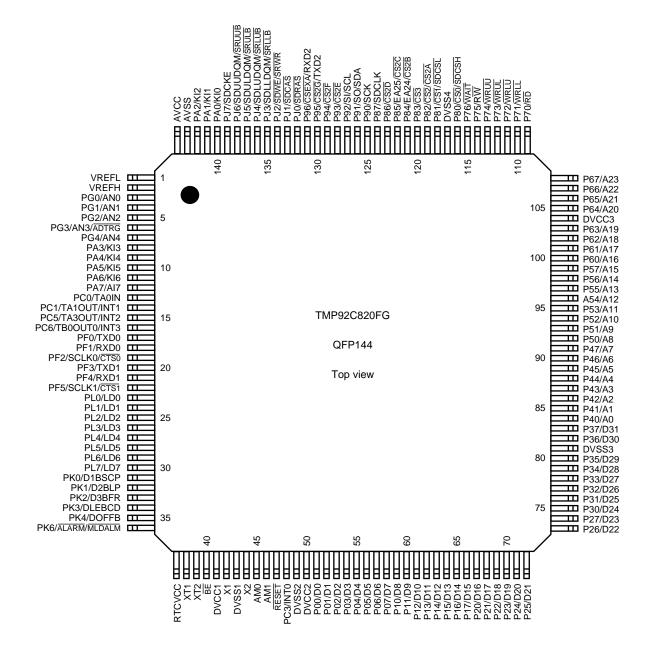

Figure 2.1.1 shows the pin assignment of the TMP92C820FG.

Figure 2.1.1 Pin Assignment Diagram (144-pin QFP)

92C820-5 2007-02-16

# 2.2 PAD Layout

Table 2.2.1 PAD Layout (144-pin chip)

(Chip size  $4.68 \text{ mm} \times 4.68 \text{ mm}$ )

Unit: µm

| (Chip size 4.68 mm × 4.68 mm) |        |         |         |            |       |         |         | Unit: µm   |       |         |         |

|-------------------------------|--------|---------|---------|------------|-------|---------|---------|------------|-------|---------|---------|

| Pin<br>No.                    | Name   | X Point | Y Point | Pin<br>No. | Name  | X Point | Y Point | Pin<br>No. | Name  | X Point | Y Point |

| 1                             | VREFL  | -2213   | 1945    | 49         | DVSS2 | -440    | -2213   | 97         | P55   | 2211    | 685     |

| 2                             | VREFH  | -2213   | 1820    | 50         | DVCC2 | -340    | -2213   | 98         | P56   | 2211    | 789     |

| 3                             | PG0    | -2213   | 1694    | 51         | P00   | -240    | -2213   | 99         | P57   | 2211    | 894     |

| 4                             | PG1    | -2213   | 1568    | 52         | P01   | -140    | -2213   | 100        | P60   | 2211    | 1000    |

| 5                             | PG2    | -2213   | 1460    | 53         | P02   | -40     | -2213   | 101        | P61   | 2211    | 1107    |

| 6                             | PG3    | -2213   | 1353    | 54         | P03   | 59      | -2213   | 102        | P62   | 2211    | 1213    |

| 7                             | PG4    | -2213   | 1249    | 55         | P04   | 160     | -2213   | 103        | P63   | 2211    | 1321    |

| 8                             | PA3    | -2213   | 1050    | 56         | P05   | 260     | -2213   | 104        | DVCC3 | 2211    | 1430    |

| 9                             | PA4    | -2213   | 946     | 57         | P06   | 360     | -2213   | 105        | P64   | 2211    | 1546    |

| 10                            | PA5    | -2213   | 842     | 58         | P07   | 460     | -2213   | 106        | P65   | 2211    | 1672    |

| 11                            | PA6    | -2213   | 739     | 59         | P10   | 561     | -2213   | 107        | P66   | 2211    | 1798    |

| 12                            | PA7    | -2213   | 635     | 60         | P11   | 661     | -2213   | 108        | P67   | 2211    | 1924    |

| 13                            | PC0    | -2213   | 531     | 61         | P12   | 761     | -2213   | 109        | P70   | 1925    | 2211    |

| 14                            | PC1    | -2213   | 427     | 62         | P13   | 861     | -2213   | 110        | P71   | 1800    | 2211    |

| 15                            | PC5    | -2213   | 326     | 63         | P14   | 961     | -2213   | 111        | P72   | 1675    | 2211    |

| 16                            | PC6    | -2213   | 224     | 64         | P15   | 1062    | -2213   | 112        | P73   | 1558    | 2211    |

| 17                            | PF0    | -2213   | 123     | 65         | P16   | 1162    | -2213   | 113        | P74   | 1448    | 2211    |

| 18                            | PF1    | -2213   | 23      | 66         | P17   | 1263    | -2213   | 114        | P75   | 1346    | 2211    |

| 19                            | PF2    | -2213   | -77     | 67         | P20   | 1363    | -2213   | 115        | P76   | 1243    | 2211    |

| 20                            | PF3    | -2213   | -179    | 68         | P21   | 1474    | -2213   | 116        | P80   | 1141    | 2211    |

| 21                            | PF4    | -2213   | -284    | 69         | P22   | 1589    | -2213   | 117        | DVSS4 | 1038    | 2211    |

| 22                            | PF5    | -2213   | -388    | 70         | P23   | 1702    | -2213   | 118        | P81   | 937     | 2211    |

| 23                            | PL0    | -2213   | -493    | 71         | P24   | 1814    | -2213   | 119        | P82   | 835     | 2211    |

| 24                            | PL1    | -2213   | -598    | 72         | P25   | 1926    | -2213   | 120        | P83   | 734     | 2211    |

| 25                            | PL2    | -2213   | -704    | 73         | P26   | 2211    | -1924   | 121        | P84   | 633     | 2211    |

| 26                            | PL3    | -2213   | -809    | 74         | P27   | 2211    | -1799   | 122        | P85   | 532     | 2211    |

| 27                            | PL4    | -2213   | -914    | 75         | P30   | 2211    | -1674   | 123        | P86   | 431     | 2211    |

| 28                            | PL5    | -2213   | -1024   | 76         | P31   | 2211    | -1548   | 124        | P87   | 330     | 2211    |

| 29                            | PL6    | -2213   | -1132   | 77         | P32   | 2211    | -1426   | 125        | P90   | 229     | 2211    |

| 30                            | PL7    | -2213   | -1243   | 78         | P33   | 2211    | -1311   | 126        | P91   | 128     | 2211    |

| 31                            | PK0    | -2213   | -1354   | 79         | P34   | 2211    | -1199   | 127        | P92   | 28      | 2211    |

| 32                            | PK1    | -2213   | -1464   | 80         | P35   | 2211    | -1087   | 128        | P93   | -72     | 2211    |

| 33                            | PK2    | -2213   | -1576   | 81         | DVSS3 | 2211    | -975    | 129        | P94   | -173    | 2211    |

| 34                            | PK3    | -2213   | -1701   | 82         | P36   | 2211    | -864    | 130        | P95   | -274    | 2211    |

| 35                            | PK4    | -2213   | -1826   | 83         | P37   | 2211    | -757    | 131        | P96   | -375    | 2211    |

| 36                            | PK6    | -2213   | -1953   | 84         | P40   | 2211    | -648    | 132        | PJ0   | -477    | 2211    |

| 37                            | RTCVCC | -1962   | -2213   | 85         | P41   | 2211    | -541    | 133        | PJ1   | -580    | 2211    |

| 38                            | XT1    | -1851   | -2213   | 86         | P42   | 2211    | -435    | 134        | PJ2   | -684    | 2211    |

| 39                            | XT2    | -1574   | -2213   | 87         | P43   | 2211    | -332    | 135        | PJ3   | -788    | 2211    |

| 40                            | BE     | -1466   | -2213   | 88         | P44   | 2211    | -228    | 136        | PJ4   | -892    | 2211    |

| 41                            | DVCC1  | -1360   | -2213   | 89         | P45   | 2211    | -128    | 137        | PJ5   | -996    | 2211    |

| 42                            | X1     | -1257   | -2213   | 90         | P46   | 2211    | -28     | 138        | PJ6   | -1101   | 2211    |

| 43                            | DVSS1  | -1057   | -2213   | 91         | P47   | 2211    | 71      | 139        | PJ7   | -1208   | 2211    |

| 44                            | X2     | -957    | -2213   | 92         | P50   | 2211    | 171     | 140        | PA0   | -1319   | 2211    |

| 45                            | AM0    | -840    | -2213   | 93         | P51   | 2211    | 272     | 141        | PA1   | -1430   | 2211    |

| 46                            | AM1    | -740    | -2213   | 94         | P52   | 2211    | 374     | 142        | PA2   | -1555   | 2211    |

| 47                            | RESET  | -640    | -2213   | 95         | P53   | 2211    | 477     | 143        | AVSS  | -1828   | 2211    |

| 48                            | PC3    | -540    | -2213   | 96         | P54   | 2211    | 581     | 144        | AVCC  | -1955   | 2211    |

|                               |        |         | •       |            |       |         |         |            |       |         |         |

## 2.3 Pin Names and Functions

The following table shows the names and functions of the input/output pins.

Table 2.3.1 Pin Names and Functions (1/3)

|                          | Number of |                  | Table 2.3.1 Pin Names and Functions (1/3)                                                                                                                        |

|--------------------------|-----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Names                | Pins      | I/O              | Functions                                                                                                                                                        |

| D0 to D7                 | 8         | I/O              | Data: Data bus 0 to 7.                                                                                                                                           |

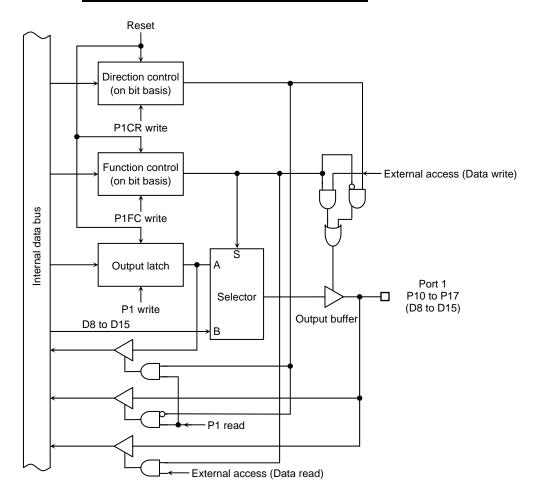

| P10 to P17               | 8         | I/O              | Port 1: I/O port. Input or output specifiable in units of bits.                                                                                                  |

| D8 to D15                |           | I/O              | Data: Data bus 8 to 15.                                                                                                                                          |

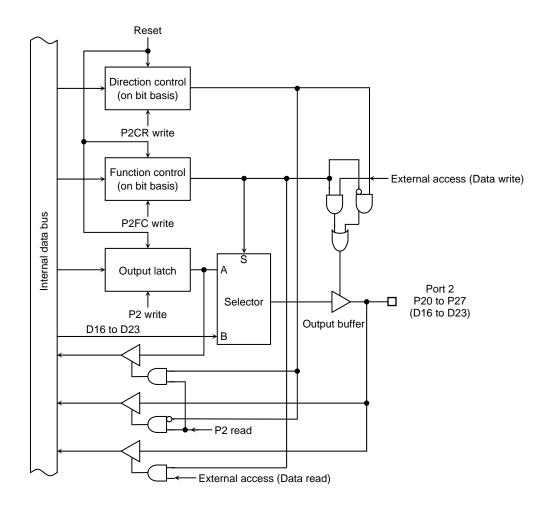

| P20 to P27               | 8         | I/O              | Port 2: I/O port. Input or output specifiable in units of bits.                                                                                                  |

| D16 to D23               | 0         | 1/0              | Data: Data bus 16 to 23.                                                                                                                                         |

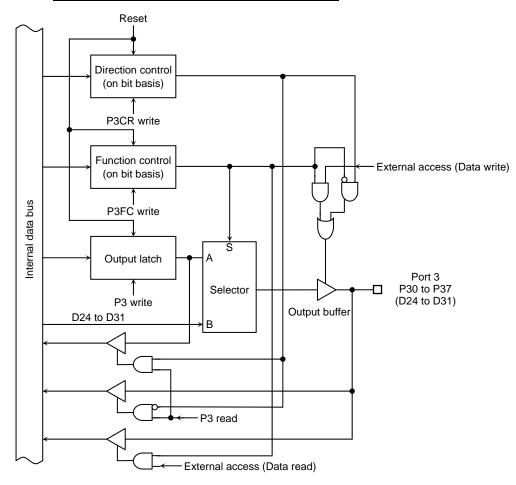

| P30 to P37               | 8         | I/O              | Port 3: I/O port. Input or output specifiable in units of bits.                                                                                                  |

| D24 to D31               |           | 1/0              | Data: Data bus 24 to 31.                                                                                                                                         |

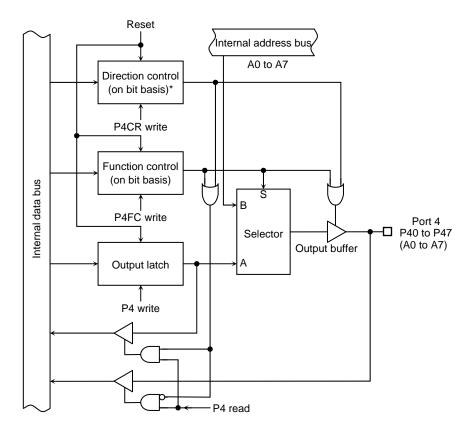

| P40 to P47<br>A0 to A7   | 8         | 1/0              | Port 4: I/O port. Input or output specifiable in units of bits.                                                                                                  |

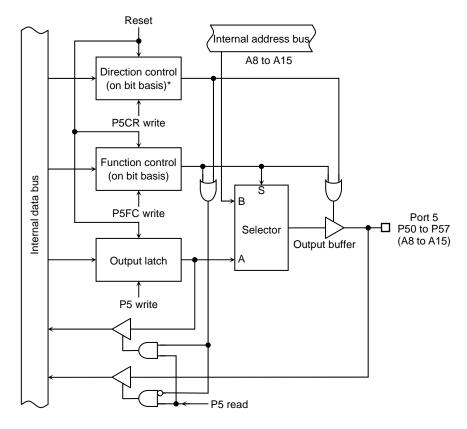

| P50 to P57               | 0         | Output           | Address: Address bus 0 to 7.                                                                                                                                     |

| A8 to A15                | 8         | I/O              | Port 5: I/O port. Input or output specifiable in units of bits.                                                                                                  |

|                          | 0         | Output           | Address: Address bus 8 to 15.                                                                                                                                    |

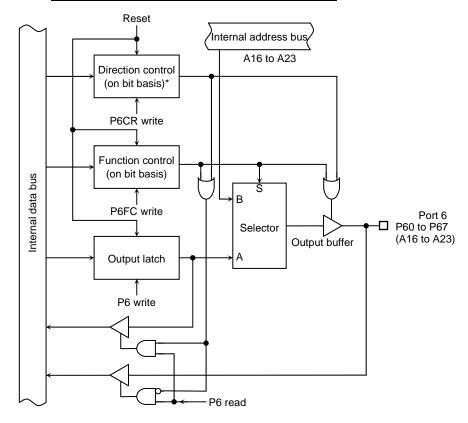

| P60 to P67<br>A16 to A23 | 8         | 1/0              | Port 6: I/O port. Input or output specifiable in units of bits.                                                                                                  |

|                          | 4         | Output           | Address: Address bus 16 to 23.                                                                                                                                   |

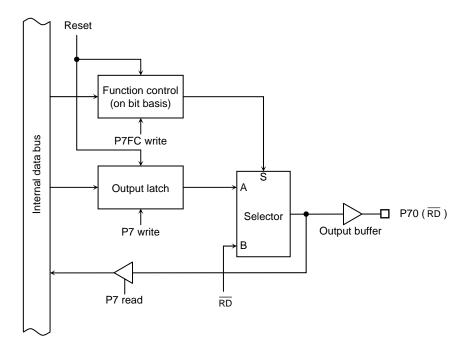

| P70<br>RD                | 1         | Output           | Port 70: Output port                                                                                                                                             |

|                          | 4         | Output           | Read: Outputs strobe signal to read external memory.                                                                                                             |

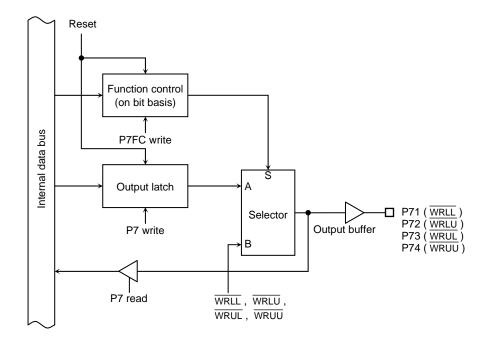

| P71<br>WRLL              | 1         | Output           | Port 71: Output port                                                                                                                                             |

|                          | 4         | Output           | Write: Output strobe signal for writing data on pins D0 to D7.                                                                                                   |

| P72<br>WRLU              | 1         | Output           | Port 72: Output port                                                                                                                                             |

|                          | 4         | Output           | Write: Output strobe signal for writing data on pins D8 to D15.                                                                                                  |

| P73<br>WRUL              | 1         | Output           | Port 73: Output port                                                                                                                                             |

|                          | 4         | Output           | Write: Output strobe signal for writing data on pins D16 to D23.                                                                                                 |

| P74<br>WRUU              | 1         | Output           | Port 74: Output port                                                                                                                                             |

|                          | 4         | Output           | Write: Output strobe signal for writing data on pins D24 to D31.                                                                                                 |

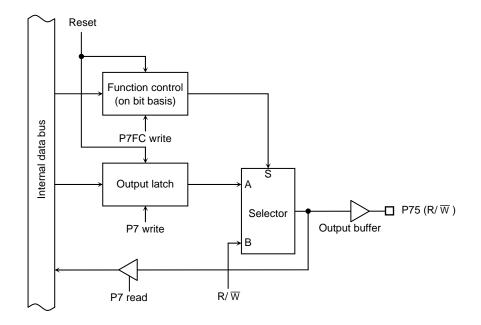

| P75<br>R/ ₩              | 1         | Output           | Port 75: Output port                                                                                                                                             |

| P76                      | 1         | Output           | Read/Write: 1 represents read or dummy cycle; 0 represents write cycle.                                                                                          |

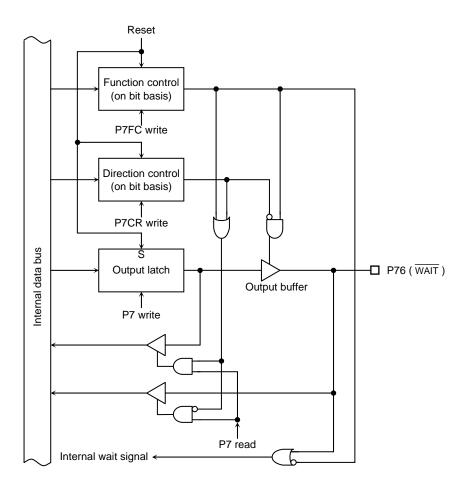

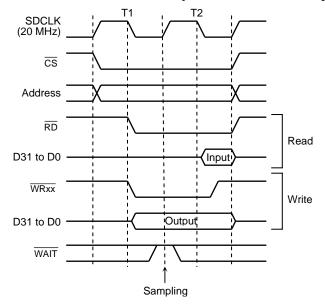

| WAIT                     | l         | I/O              | Port 76: I/O port                                                                                                                                                |

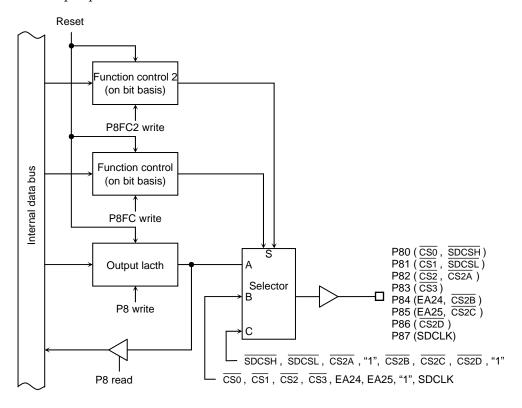

| P80                      |           | Input            | Wait: Signal used to request CPU bus wait.                                                                                                                       |

| CS0                      | 1         | Output<br>Output | Port 80: Output port                                                                                                                                             |

| SDCSH                    | l         | Output           | Chip select 0: Outputs "low" when address is within specified address area.  Chip select for SDRAM: Outputs "0" when address is within SDRAM upper-address area. |

| P81                      |           | Output           | Port 81: Output port                                                                                                                                             |

| <del>CS1</del>           | 1         | Output           | Chip select 1: Outputs "low" when address is within specified address area.                                                                                      |

| SDCSL                    | ı         | Output           | Chip select for SDRAM: Outputs "0" when address is within SDRAM lower-address area.                                                                              |

| P82                      |           |                  |                                                                                                                                                                  |

| CS2                      | 1         | Output<br>Output | Port 82: Output port  Chip select 2: Outputs "low" when address is within specified address area.                                                                |

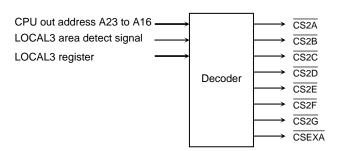

| CS2A                     |           | Output           | Expand chip select 2A: Outputs "0" when address is within specified address area.                                                                                |

| P83                      |           | Output           | Port 83: Output port                                                                                                                                             |

| <u>CS3</u>               | 1         | Output           | Chip select 3: Outputs "low" when address is within specified address area.                                                                                      |

| P84                      |           | Output           | Port 84: Output port                                                                                                                                             |

| EA24                     | 1         | Output           | Chip select 24: Outputs "0" when address is within specified address area.                                                                                       |

| CS2B                     | ,         | Output           | Expand chip select 2B: Outputs "0" when address is within specified address area.                                                                                |

| P85                      |           | Output           | Port 85: Output port                                                                                                                                             |

| EA25                     | 1         | Output           | Chip select 25: Outputs "0" when address is within specified address area.                                                                                       |

| CS2C                     |           | Output           | Expand chip select 2C: Outputs "0" when address is within specified address area.                                                                                |

| P86                      |           | Output           | Port 86: Output port                                                                                                                                             |

| CS2D                     | 1         | Output           | Expand chip select 2D: Outputs "0" when address is within specified address area.                                                                                |

| P87                      |           | Output           | Port 87: Output port                                                                                                                                             |

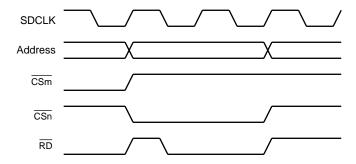

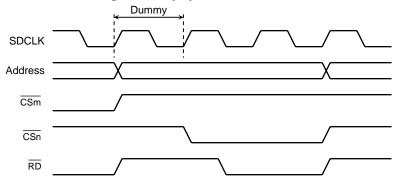

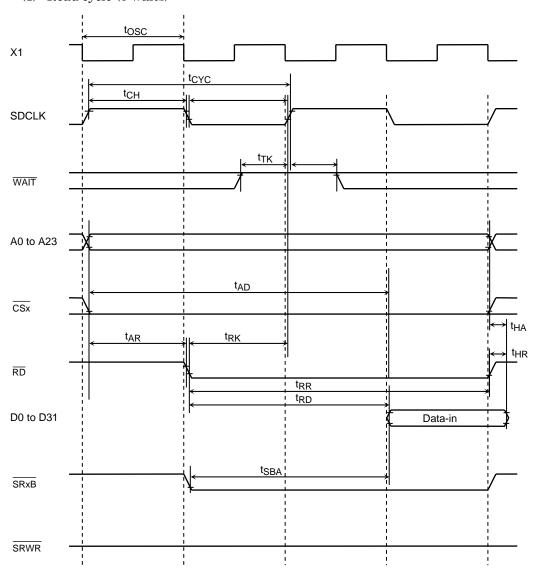

| SDCLK                    | 1         | Output           | Clock for SDRAM                                                                                                                                                  |

|                          |           | - 21,701         |                                                                                                                                                                  |

Table 2.3.1 Pin Names and Functions (2/3)

| Pin Names        | Number of Pins | I/O           | Functions                                                                                   |

|------------------|----------------|---------------|---------------------------------------------------------------------------------------------|

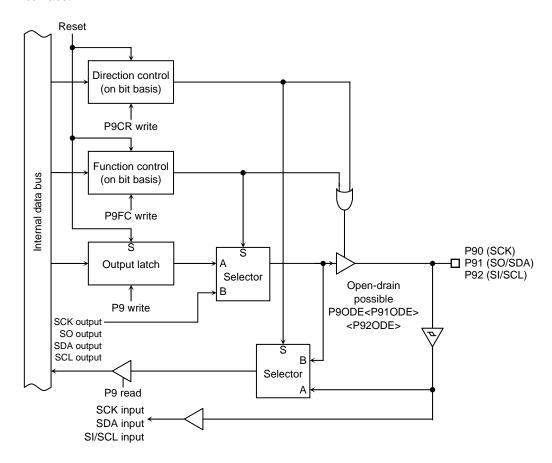

| P90              | 1              | I/O           | Port 90: I/O port                                                                           |

| SCK              | •              | I/O           | Serial bus interface clock I/O data at SIO mode.                                            |

| P91              |                | I/O           | Port 91: I/O port                                                                           |

| SO               | 1              | Output        | Serial bus interface send data at SIO mode.                                                 |

| SDA              | '              | I/O           | Serial bus interface send/receive data at I <sup>2</sup> C mode.                            |

|                  |                |               | (Open drain/output mode by programmable.)                                                   |

| P92              |                | I/O           | Port 92: I/O port                                                                           |

| SI               | 1              | Input         | Serial bus interface receive data at SIO mode.                                              |

| SCL              | '              | I/O           | Serial bus interface clock I/O data at I <sup>2</sup> C mode.                               |

|                  |                |               | (Open drain/output mode by programmable.)                                                   |

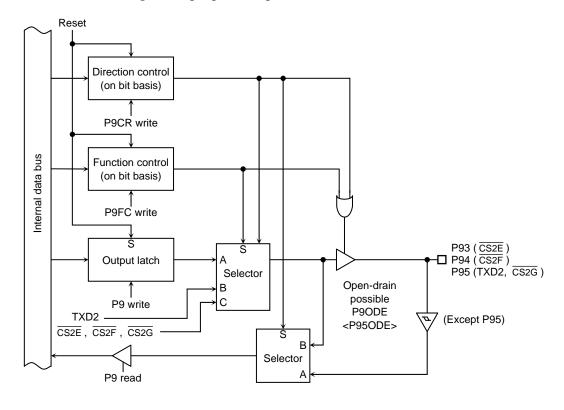

| P93              | 1              | I/O           | Port 93: I/O port                                                                           |

| CS2E             | -              | Output        | Expand chip select 2E: Outputs "0" when address is within specified address area.           |

| P94              | 4              | I/O           | Port 94: I/O port                                                                           |

| CS2F             | 1              | Output        | Expand chip select 2F: Outputs "0" when address is within specified address area.           |

| P95              |                | I/O           | Port 95: Output port                                                                        |

| CS2G             | 1              | Output        | Expand chip select 2G: Outputs "0" when address is within specified address area.           |

| TXD2             |                | Output        | Serial transmission data 2. Open drain/output pin by programmable.                          |

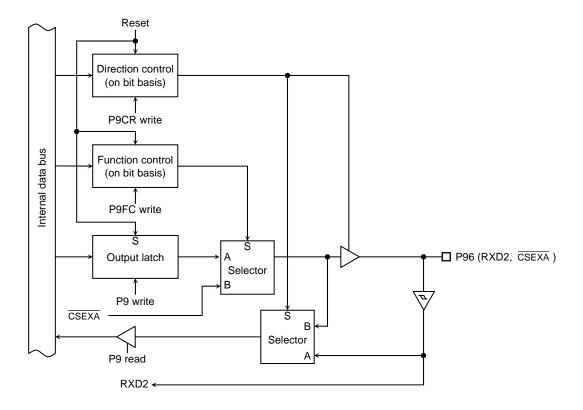

| P96              |                | I/O           | Port 96: Output port                                                                        |

| RXD2             | 1              | Input         | Serial receive data 2.                                                                      |

| CSEXA            |                | Output        | Expand chip select EXA: Outputs "0" when address is within specified address area.          |

| PA0 to PA7       |                | Input         | A0 to A7 port: Pin used to input ports.                                                     |

| KI0 to KI7       | 8              | Input         | Key input 0 to 7: Pin used of key-on wakeup 0 to 7.                                         |

|                  |                |               | (Schmitt input, with pull-up resistor.)                                                     |

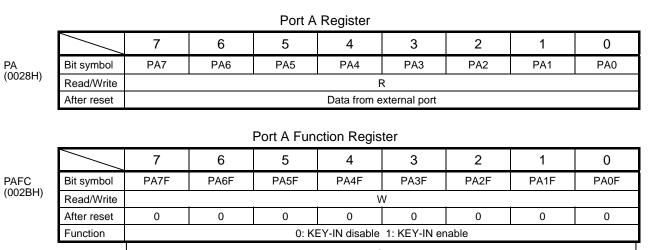

| PC0              |                | I/O           | Port C0: I/O port                                                                           |

| TAOIN            | 1              | Input         | 8-bit timer 0 input: Timer 0 input.                                                         |

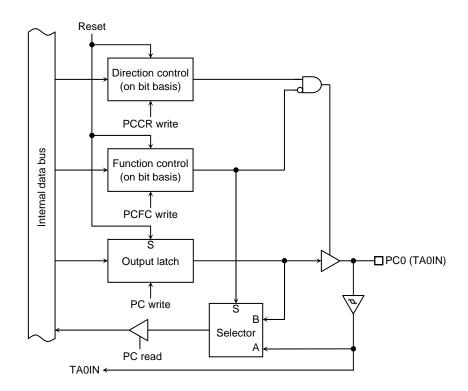

| PC1              |                | I/O           | Port C1: I/O port                                                                           |

| INT1             | 1              | Input         | Interrupt request pin1 : Interrupt request pin with programmable rising /falling edge.      |

| TA1OUT           | •              | Output        | 8-bit timer 1 output: Timer 1 output.                                                       |

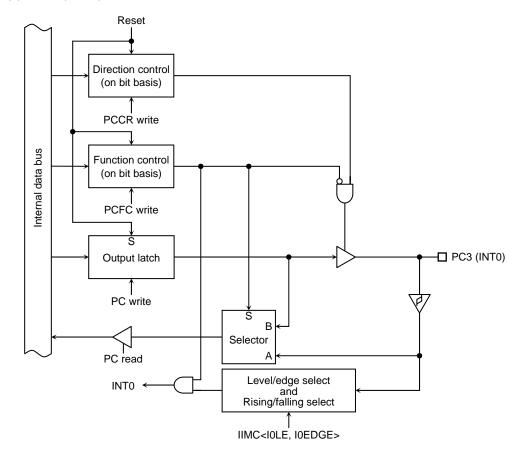

| PC3              |                | I/O           | Port C3: I/O port                                                                           |

| INTO             | 1              | Input         | Interrupt request pin 0: Interrupt request pin with programmable level/rising/falling edge. |

| PC5              |                | I/O           | Port C5: I/O port                                                                           |

| INT2             | 1              | Input         | Interrupt request pin 2 : Interrupt request pin with programmable rising /falling edge.     |

| TA3OUT           | ,              | Output        | 8-bit timer 3 output: Timer 3 output.                                                       |

| PC6              |                | I/O           | Port C6: I/O port                                                                           |

| INT3             | 1              | Input         | Interrupt request pin 3: Interrupt request pin with programmable rising /falling edge.      |

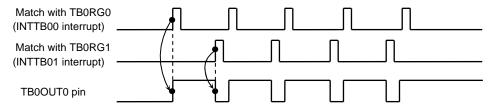

| TB0OUT0          | •              | Output        | Timer B0 output.                                                                            |

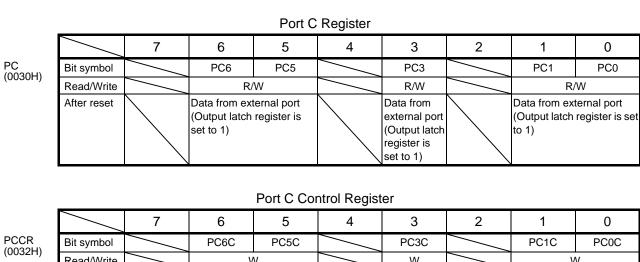

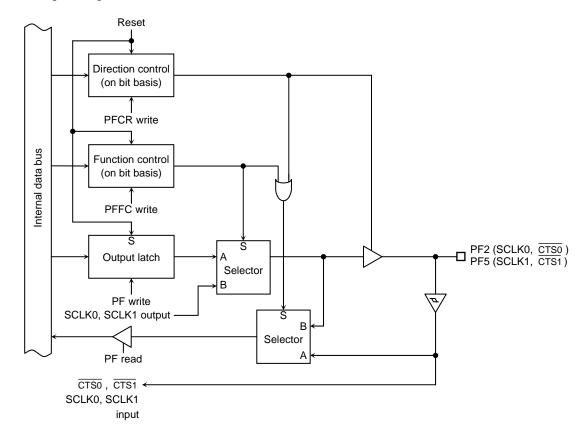

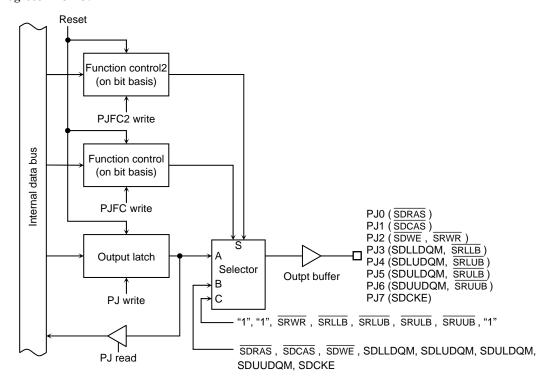

| PF0              |                | I/O           | Port F0: I/O port                                                                           |

| TXD0             | 1              | Output        | Serial 0 send data: Open drain/output pin by programmable.                                  |

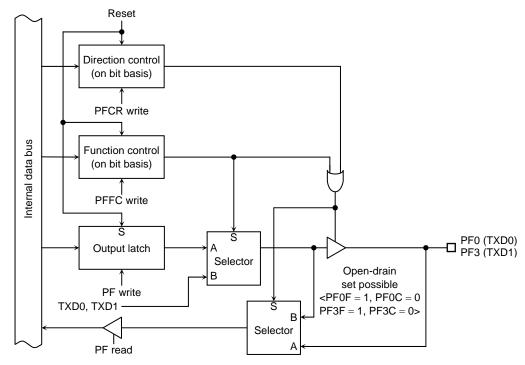

| PF1              |                | I/O           | Port F1: I/O port                                                                           |

| RXD0             | 1              | Input         | Serial 0 receive data.                                                                      |

| PF2              |                | I/O           | Port F2: I/O port                                                                           |

| SCLK0            | 1              | I/O           | Serial 0 clock I/O.                                                                         |

| CTS0             | ı              | Input         | Serial 0 data send enable (Clear to send).                                                  |

| PF3              |                | I/O           |                                                                                             |

| TXD1             | 1              |               | Port F3: I/O port Serial 1 send data: Open drain/output pin by programmable.                |

| PF4              |                | Output<br>I/O |                                                                                             |

| RXD1             | 1              |               | Port F4: I/O port                                                                           |

| PF5              |                | Input         | Serial 1 receive data.                                                                      |

| SCLK1            | 4              | 1/0           | Port F5: I/O port                                                                           |

| CTS1             | 1              | I/O           | Serial 1 clock I/O.                                                                         |

|                  |                | Input         | Serial 1 data send enable (Clear to send).                                                  |

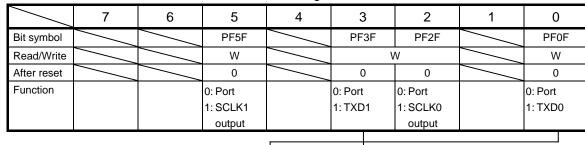

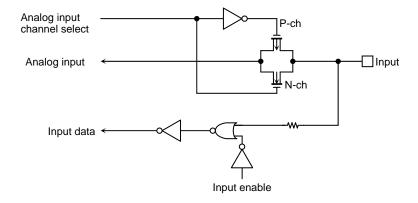

| PG0 to PG4       | _              | Input         | Port G0 to G4 port: Pin used to input ports.                                                |

| AN0 to AN4 ADTRG | 5              | Input         | Analog input 0 to 4: Pin used to Input to AD conveter.                                      |

| ADING            |                | Input         | AD trigger: Signal used to request AD start (with used to PG3).                             |

Table 2.3.1 Pin Names and Functions (3/3)

| Pin Names    | Number of Pins  | I/O              | Functions                                                                                                    |

|--------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------|

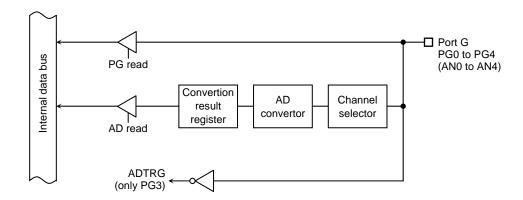

| PJ0<br>SDRAS | 1               | Output<br>Output | Port J0: Output port  Row address strobe for SDRAM: Outputs "0" when address is within SDRAM address area.   |

| PJ1          |                 | •                | ·                                                                                                            |

| SDCAS        | 1               | Output<br>Output | Port J1: Output port Column address strobe for SDRAM: Outputs "0" when address is within SDRAM address area. |

| PJ2          |                 | Output           | Port J2: Output port                                                                                         |

| SDWE         | 1               | Output           | Write enable for SDRAM.                                                                                      |

| SRWR         |                 | Output           | Write for SRAM: Strobe signal for writing data .                                                             |

| PJ3          |                 | Output           | Port J3: Output port                                                                                         |

| SDLLDQM      | 1               | Output           | Data enable for SDRAM on pins D0 to D7.                                                                      |

| SRLLB        |                 | Output           | Data enable for SRAM on pins D0 to D7.                                                                       |

| PJ4          |                 | Output           | Port J4: Output port                                                                                         |

| SDLUDQM      | 1               | Output           | Data enable for SDRAM on pins D8 to D15.                                                                     |

| SRLUB        |                 | Output           | Data enable for SRAM on pins D8 to D15.                                                                      |

| PJ5          |                 | Output           | Port J5: Output port                                                                                         |

| SDULDQM      | 1               | Output           | Data enable for SDRAM on pins D16 to D23.                                                                    |

| SRULB        |                 | Output           | Data enable for SRAM on pins D16 to D23.                                                                     |

| PJ6          |                 | Output           | Port J6: Output port                                                                                         |

| SDUUDQM      | 1               | Output           | Data enable for SDRAM on pins D24 to D32.                                                                    |

| SRUUB        |                 | Output           | Data enable for SRAM on pins D24 to D32.                                                                     |

| PJ7          | 4               | Output           | Port J7: Output port                                                                                         |

| SDCKE        | 1               | Output           | Clock enable for SDRAM.                                                                                      |

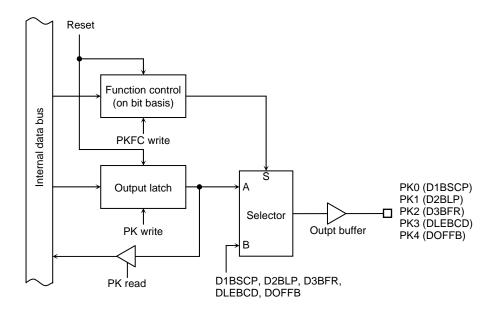

| PK0          | 4               | Output           | Port K0: Output port                                                                                         |

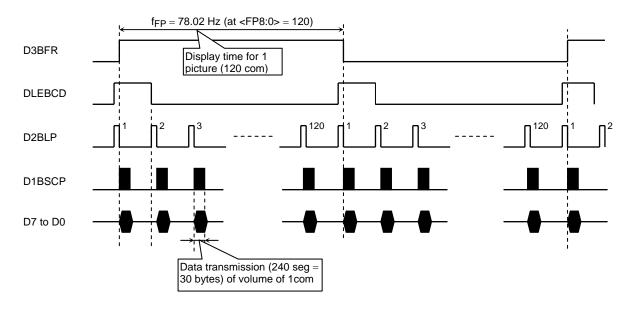

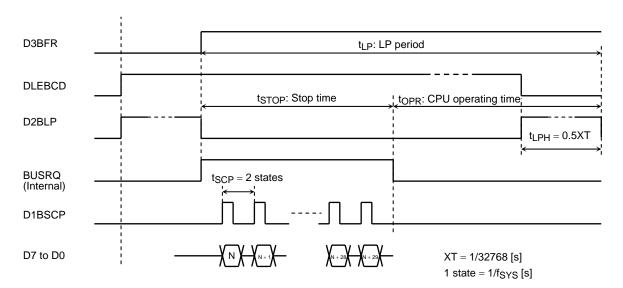

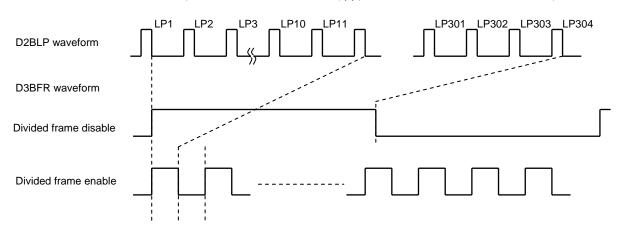

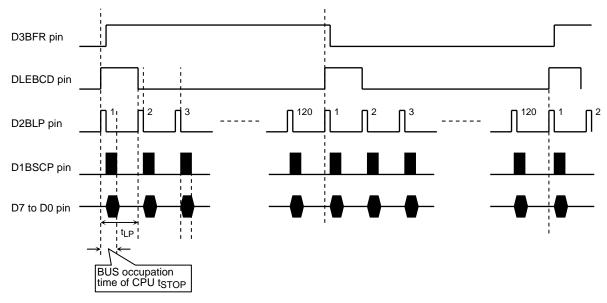

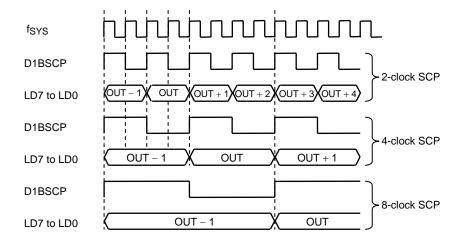

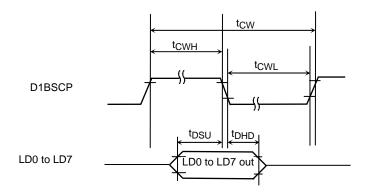

| D1BSCP       | 1               | Output           | LCD driver output pin.                                                                                       |

| PK1          | 1 Output Output |                  | Port K1: Output port                                                                                         |

| D2BLP        |                 |                  | LCD driver output pin.                                                                                       |

| PK2          | 4               | Output           | Port K2: Output port                                                                                         |

| D3BFR        | 1               | Output           | LCD driver output pin.                                                                                       |

| PK3          | 4               | Output           | Port K3: Output port                                                                                         |

| DLEBCD       | 1               | Output           | LCD driver output pin.                                                                                       |

| PK4          | 4               | Output           | Port K4: Output port                                                                                         |

| DOFFB        | 1               | Output           | LCD driver output pin.                                                                                       |

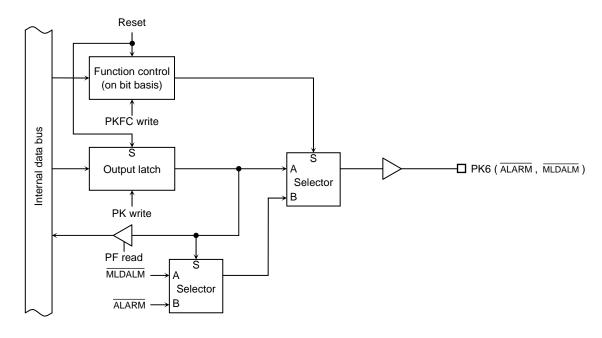

| PK6          |                 | Output           | Port K6: Output port                                                                                         |

| ALARM        | 1               | Output           | RTC alarm output pin.                                                                                        |

| MLDALM       |                 | Output           | Melody/alarm output pin (Inverted).                                                                          |

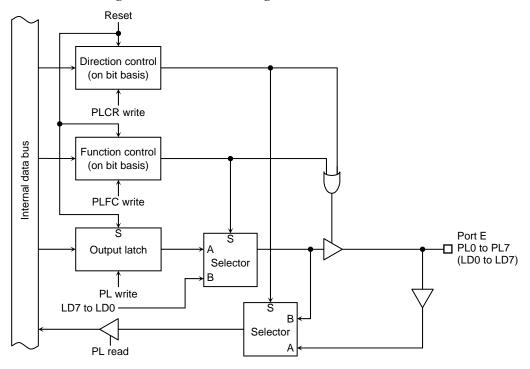

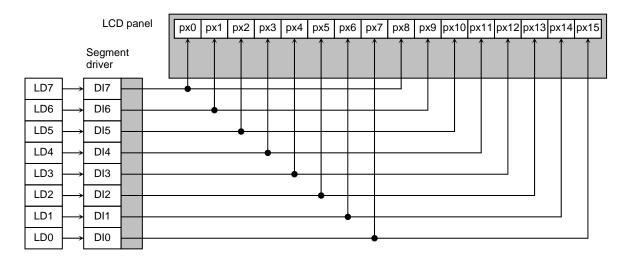

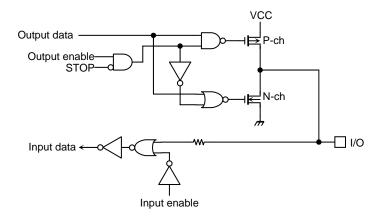

| PL0 to PL7   | 0               | I/O              | Port L0 to L7: I/O port                                                                                      |

| LD0 to LD7   | 8               | Output           | Data bus for LCD driver.                                                                                     |

| BE           | 1               | Input            | Backup enable.                                                                                               |

|              |                 |                  | Operation mode:                                                                                              |

| AM0, AM1     | 2               | Input            | Fix to AM1 = "0", AM0 = "1": 16-bit external bus or 8-/16-/32-bit dynamic sizing.                            |

|              |                 | -                | Fix to AM1 = "1", AM0 = "0": 32-bit external bus or 8-/16-/32-bit dynamic sizing.                            |

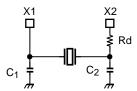

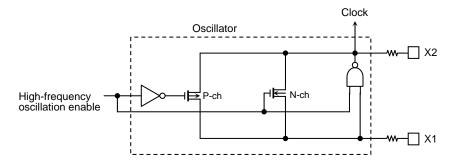

| X1/X2        | 2               | I/O              | High-frequency oscillator connection pins.                                                                   |

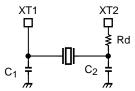

| XT1/XT2      | 2               | I/O              | Low-frequency oscillator connection pins.                                                                    |

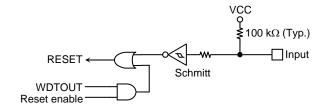

| RESET        | 1               | Input            | Reset: Initializes TMP92C820 (with pull-up resistor).                                                        |

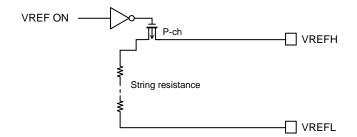

| VREFH        | 1               | Input            | Pin for reference voltage input to AD converter (H).                                                         |

| VREFL        | 1               | Input            | Pin for reference voltage input to AD converter (L).                                                         |

| AVCC         | 1               | -                | Power supply pin for AD converter.                                                                           |

| AVSS         | 1               | _                | GND pin for AD converter (0 V).                                                                              |

| DVCC         | 3               | =                | Power supply pins (All DVCC pins should be connected with the power supply pin).                             |

| DVSS         | 4               |                  | GND pins (0 V) (All DVSS pins should be connected with GND (0V)).                                            |

| RTCVCC       | 1               |                  | Power supply pin for RTC and low-frequency oscillator.                                                       |

|              | ı               |                  | . One. supply parties in the data low inequency oscillator.                                                  |

# 3. Operation

This section describes the basic components, functions and operation of the TMP92C820.

#### 3.1 CPU

The TMP92C820 contains an advanced high-speed 32-bit CPU (900/H1 CPU). For CPU operation, see the TLCS-900/H1 CPU.

The following describe the unique function of the CPU used in the TMP92C820; these functions are not covered in the TLCS-900/H1 CPU section.

## 3.1.1 CPU Outline

900/H1 CPU is high-speed and high-performance CPU based on 900/L1 CPU. 900/H1 CPU has expanded 32-bit internal data bus to process instructions more quickly. Outline of 900/H1 CPU are as follows:

Table 3.1.1 CPU Outline

|                              | 900/H1 CPL                |                             |                      |  |  |  |

|------------------------------|---------------------------|-----------------------------|----------------------|--|--|--|

| Width of CPU address bus     | 24 bits                   |                             |                      |  |  |  |

| Width of CPU data bus        | 32 bits                   |                             |                      |  |  |  |

| Internal operating frequency | 20 MHz                    |                             |                      |  |  |  |

| Minimum bus cycle            | 1-clock acce              | ss (50 ns at 20 MHz)        |                      |  |  |  |

| Data bus sizing              | 8/16/32 bits              |                             |                      |  |  |  |

| Internal RAM                 | 32 bits                   |                             |                      |  |  |  |

|                              | 1-clock acce              | ess                         |                      |  |  |  |

| Internal I/O                 | 8-/16-bit                 | 2-clock access              | 900/H1 I/O           |  |  |  |

|                              | 8-/16-bit                 | 5 to 6-clock access         | 900/L1 I/O           |  |  |  |

| External device              | 8 bits                    |                             |                      |  |  |  |

|                              | 2-clock acce              | ss (can insert some waits.) |                      |  |  |  |

| Minimum instruction          | 1 clock (50 ns at 20 MHz) |                             |                      |  |  |  |

| Execution cycle              |                           |                             |                      |  |  |  |

| Conditional jump             | 2 clocks (10              | 0 ns at 20 MHz)             |                      |  |  |  |

| Instruction queue buffer     | 12 bytes                  |                             |                      |  |  |  |

| Instruction set              | Compatible                | with TLCS-900, 900/L, 900/  | H, 900/L1 and 900/H2 |  |  |  |

|                              | (NORMAL, I                | MAX, MIN and LDX instruct   | ion is deleted.)     |  |  |  |

| CPU mode                     | Only maximum mode         |                             |                      |  |  |  |

| Micro DMA                    | 8 channels                |                             |                      |  |  |  |

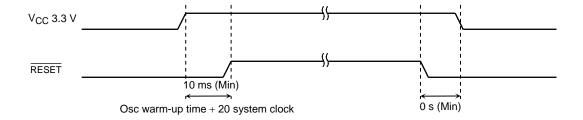

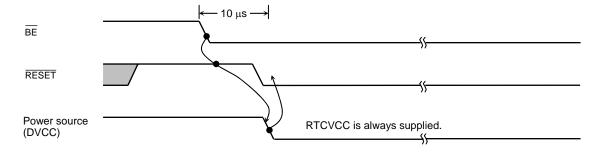

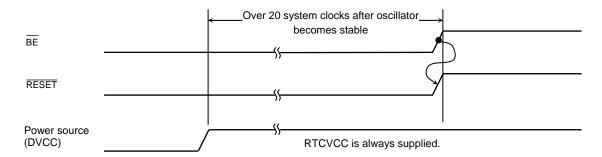

#### 3.1.2 Reset Operation

When resetting the TMP92C820 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input low for at least 20 system clocks (16  $\mu$ s at 40 MHz).

When the reset has been accepted, the CPU performs the following:

Sets the program counter (PC) as follows in accordance with the reset vector stored at address FFFF00H to FFFF02H:

PC<7:0> ← Data in location FFFF00H

PC<15:8> ← Data in location FFFF01H

PC<23:16> ← Data in location FFFF02H

- Sets the stack pointer (XSP) to 00000000H.

- Sets bits <IFF0:2> of the status register (SR) to 111 (Thereby setting the interrupt level mask register to level 7).

- Clears bits <RFP0:1> of the status register to 00 (Thereby selecting register bank0).

When the reset is released, the CPU starts executing instructions according to the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports and other pins as follows.

- Initializes the internal I/O registers as table of "Table of Special Function Registers (SFRs)" in section 5.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose input or output port mode.

Internal RESET is released as soon as external reset is released.

The operation of memory controller cannot be insured until power supply becomes stable after power-on reset. The external RAM data provided before turning on the TMP92C820 may be spoiled because the control signals are unstable until power supply becomes stable after power on reset.

Figure 3.1.1 Power on Reset Timing Example

# 3.1.3 Setting of AM0 and AM1

Set AM1 and AM0 pins to "10" to use 32-bit external bus, or set it to "01" to use 16-bit external bus.

Table 3.1.2 Operation Mode Setup Table

| Operation Mode                   | Mode Setup Input Pin |     |     |  |  |

|----------------------------------|----------------------|-----|-----|--|--|

| Operation Mode                   | RESET                | AM1 | AM0 |  |  |

| 16-bit external bus              |                      |     |     |  |  |

| or                               |                      | 0   | 1   |  |  |

| 8-/16-/32-bit dynamic bus sizing | 1                    |     |     |  |  |

| 32-bit external bus              |                      |     |     |  |  |

| or                               |                      | 1   | 0   |  |  |

| 8-/16-/32-bit dynamic bus sizing |                      |     |     |  |  |

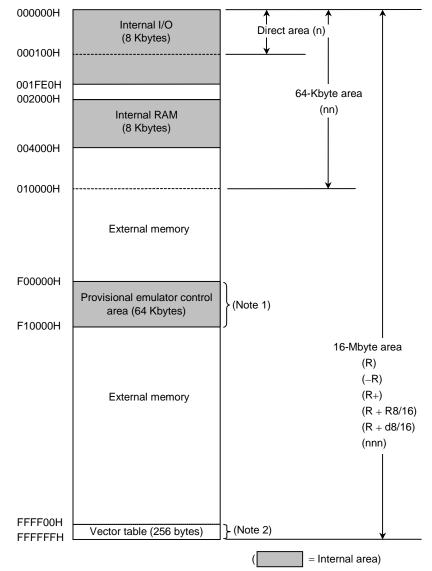

## 3.2 Memory Map

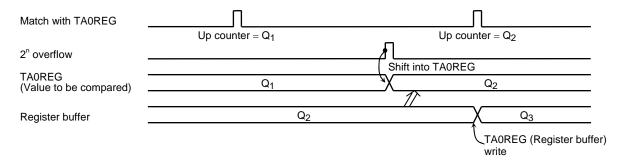

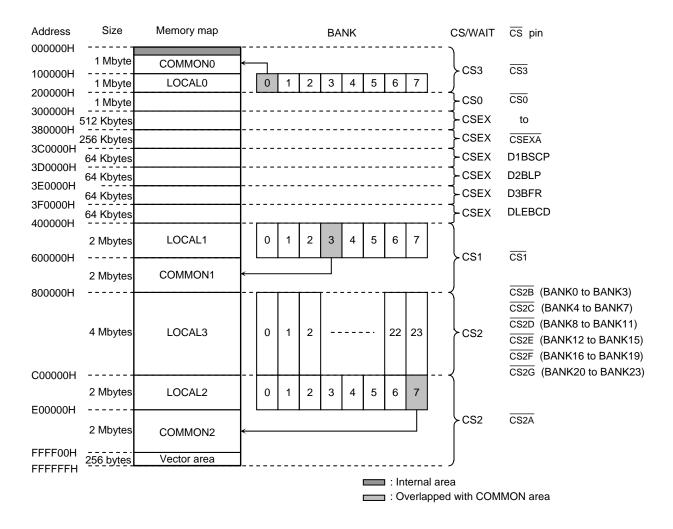

Figure 3.2.1 is a memory map of the TMP92C820.

- Note 1: Provisional emulator control area is for emulator, it is mapped F00000H to F10000H address after reset.

- Note 2: Don't use the last 16-byte area (FFFFF0H to FFFFFFH). This area is reserved.

- Note 3: On emulator  $\overline{WR}$  signal and  $\overline{RD}$  signal are asserted, when provisional emulator control area is accessed. Be careful to use external memory.

Figure 3.2.1 Memory Map

# 3.3 Clock Function and Standby Function

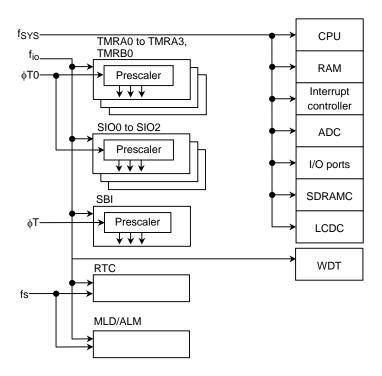

TMP92C820 contains (1) Clock gear, (2) Standby controller, and (3) Noise reduction circuit. It is used for low-power, low-noise systems.

This chapter is organized as follows:

- 3.3.1 Block Diagram of System Clock

- 3.3.2 SFR

- 3.3.3 System Clock Controller

- 3.3.4 Noise Reduction Circuits

- 3.3.5 Standby Controller

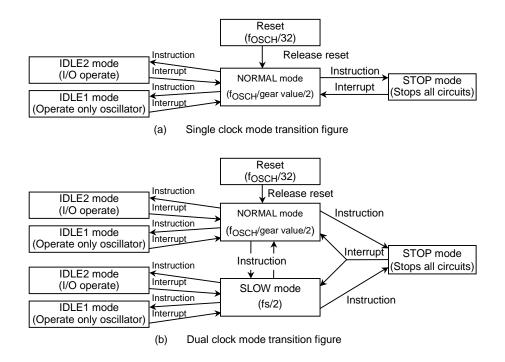

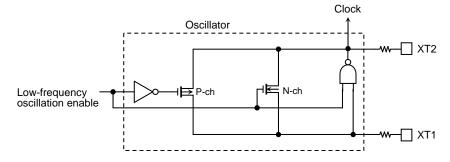

The clock operating modes are as follows: (a) Single clock mode (X1, X2 pins only) and (b) Dual clock mode (X1, X2, XT1, and XT2 pins).

Figure 3.3.1 shows a transition figure.

Figure 3.3.1 System Clock Block Diagram

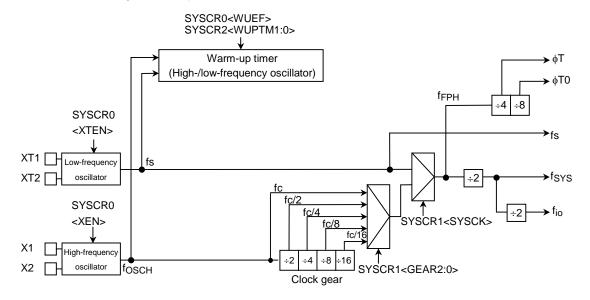

The clock frequency input from the X1 and X2 pins is called fc and the clock frequency input from the XT1 and XT2 pins is called fs. The clock frequency selected by SYSCR1<SYSCK> is called the system clock  $f_{FPH}$ . The system clock  $f_{SYS}$  is defined as the divided clock of  $f_{FPH}$ , and one cycle of  $f_{SYS}$  is defined to as one state.

## 3.3.1 Block Diagram of System Clock

Figure 3.3.2 Block Diagram of System Clock

## 3.3.2 SFR

|         |             | 7                                                              | 6                                                             | 5                                                                                                                                                 | 4      | 3                                            | 2                                                                                  | 1                                                          | 0                                                                                                          |

|---------|-------------|----------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| SYSCR0  | Bit symbol  | XEN                                                            | XTEN                                                          |                                                                                                                                                   |        |                                              | WUEF                                                                               |                                                            |                                                                                                            |

| (10E0H) | Read/Write  | R/                                                             | W                                                             |                                                                                                                                                   |        |                                              | R/W                                                                                |                                                            |                                                                                                            |

|         | After reset | 1                                                              | 1                                                             |                                                                                                                                                   |        |                                              | 0                                                                                  |                                                            |                                                                                                            |

|         | Function    | High-frequency<br>oscillator (fc)<br>0: Stop<br>1: Oscillation | Low-frequency<br>oscillator (fs)<br>0: Stop<br>1: Oscillation |                                                                                                                                                   |        |                                              | Warm-up timer 0: Write Don't care 1: Write start timer 0: Read end warm up 1: Read |                                                            |                                                                                                            |

|         |             |                                                                |                                                               |                                                                                                                                                   |        |                                              | do not end<br>warm up                                                              |                                                            |                                                                                                            |

| SYSCR1  | Bit symbol  |                                                                |                                                               |                                                                                                                                                   |        | SYSCK                                        | GEAR2                                                                              | GEAR1                                                      | GEAR0                                                                                                      |

| (10E1H) | Read/Write  |                                                                |                                                               |                                                                                                                                                   |        |                                              | R/                                                                                 | W                                                          | l                                                                                                          |

|         | After reset |                                                                |                                                               |                                                                                                                                                   |        | 0                                            | 1                                                                                  | 0                                                          | 0                                                                                                          |

|         | Function    |                                                                |                                                               |                                                                                                                                                   |        | Select<br>system<br>clock.<br>0: fc<br>1: fs | 000: fc<br>001: fc/2<br>010: fc/4<br>011: fc/8<br>100: fc/16                       | value of high f                                            | requency (fc)                                                                                              |

|         | Bit symbol  | -                                                              |                                                               | WUPTM1                                                                                                                                            | WUPTM0 | HALTM1                                       | HALTM0                                                                             | SELDRV                                                     | DRVE                                                                                                       |

| (10E2H) | Read/Write  | R/W                                                            |                                                               | R/                                                                                                                                                |        | W                                            | <del> </del>                                                                       |                                                            |                                                                                                            |

|         | After reset | 0                                                              |                                                               | 1                                                                                                                                                 | 0      | 1                                            | 1                                                                                  | 0                                                          | 0                                                                                                          |

|         | Function    | Always write "0".                                              |                                                               | Warm-up timer 00: Reserved 01: 2 <sup>8</sup> /inputted frequency 10: 2 <sup>14</sup> /inputted frequency 11: 2 <sup>16</sup> /inputted frequency |        |                                              |                                                                                    | <drve><br/>mode<br/>select<br/>0: STOP<br/>1: IDLE1</drve> | Pin state<br>control in<br>STOP/<br>IDLE1 mode<br>0: I/O off<br>1: Remains<br>the state<br>before<br>halt. |

Note 1: The unassigned register, SYSCR0<Bit5:3>, SYSCR0<Bit1:0>, SYSCR1<Bit7:4>, and SYSCR2<Bit7:6> are read as undefined value.

Note 2: By reset, low-frequency oscillator is enabled.

Figure 3.3.3 SFR for System Clock

|                                        |                                                     | 7                                                                                                                                                                                     | 6 | 5 | 4 | 3 | 2                       | 1                                                      | 0                                                      |  |

|----------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|-------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| EMCCR0                                 | Bit symbol                                          | PROTECT                                                                                                                                                                               |   |   |   |   | EXTIN                   | DRVOSCH                                                | DRVOSCL                                                |  |

| (10E3H)                                | Read/Write                                          | R                                                                                                                                                                                     |   |   |   |   | R/W                     | R/W                                                    |                                                        |  |

|                                        | After reset                                         | 0                                                                                                                                                                                     |   |   |   |   | 0                       | 1                                                      | 1                                                      |  |

|                                        | Function                                            | Protect flag<br>0: OFF<br>1: ON                                                                                                                                                       |   |   |   |   | 1: fc external<br>clock | fc oscillator<br>drive ability<br>1: Normal<br>0: Weak | fs oscillator<br>drive ability<br>1: Normal<br>0: Weak |  |

| EMCCR1<br>(10E4H)<br>EMCCR2<br>(10E5H) | Bit symbol<br>Read/Write<br>After reset<br>Function | Switching the protect ON/OFF by write to following 1st-key, 2nd-key  1st-Key: EMCCR1 = 5AH, EMCCR2 = A5H in succession write  2nd-Key: EMCCR1 = A5H, EMCCR2 = 5AH in succession write |   |   |   |   |                         |                                                        |                                                        |  |

Figure 3.3.4 SFR for Noise-reduction

Note: In caseWhen restarting the oscillator in from the stop oscillation state (e.g. Restart restarting the oscillator in STOP mode), set EMCCR0<DRVOSCH>, <DRVOSCL>="1".

#### 3.3.3 System Clock Controller

The system clock controller generates the system clock signal (fsys) for the CPU core and internal I/O. It contains two oscillation circuits and a clock gear circuit for high-frequency (fc) operation. The register SYSCR1<SYSCK> changes the system clock to either fc or fs, SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator, and SYSCR1<GEAR2:0> sets the high-frequency clock gear to either 1, 2, 4, 8, or 16 (fc, fc/2, fc/4, fc/8, or fc/16). These functions can reduce the power consumption of the equipment in which the device is installed.

The combination of settings  $\langle XEN \rangle = 1$ ,  $\langle XTEN \rangle = 1$ ,  $\langle SYSCK \rangle = 0$  and  $\langle GEAR2:0 \rangle = 1$ 100 will cause the system clock (fsys) to be set to fc/32 (fc/16  $\times$  1/2) after reset.

For example, fsys is set to 1.25 MHz when the 40 MHz oscillator is connected to the X1 and X2 pins.

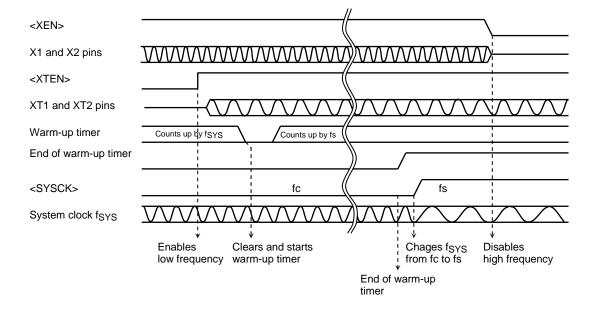

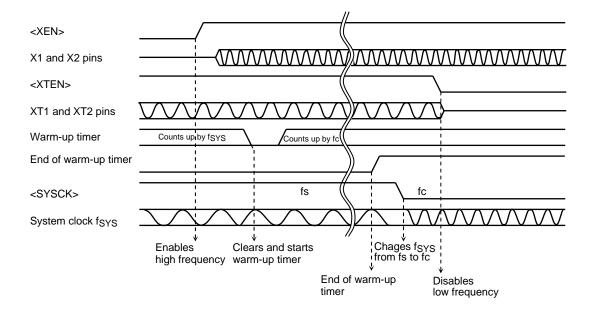

#### (1) Switching from NORMAL mode to SLOW mode

When the resonator is connected to the X1 and X2 pins, or to the XT1 and XT2 pins, the warm-up timer can be used to change the operation frequency after stable oscillation has been attained. The warm-up time can be selected using SYSCR2<WUPTM1:0>. This warm-up timer can be programmed to start and stop as shown in the following examples 1 and 2.

Table 3.3.1 shows the warm-up time.

Note 1: When using an oscillator (other than a resonator) with stable oscillation, a warm-up timer is not needed.

Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some variation in warm-up time.

| Warm-up Time<br>SYSCR2 <wuptm1:0></wuptm1:0> | Change to<br>NORMAL Mode (fc) | Change to<br>SLOW Mode (fs) | at f <sub>OSCH</sub> = 40 MHz, |

|----------------------------------------------|-------------------------------|-----------------------------|--------------------------------|

| 01 (2 <sup>8</sup> /frequency)               | 6.4 [μs]                      | 7.8 [ms]                    | fs =                           |

| 10 (2 <sup>14</sup> /frequency)              | 409.6 [μs]                    | 500 [ms]                    | 32.768 kHz                     |

| 11 (2 <sup>16</sup> /frequency)              | 1.638 [ms]                    | 2000 [ms]                   |                                |

Table 3.3.1 Warm-up Times

Example 1: Setting the clock

Changing from high frequency (fc) to low frequency (fs).

| SYSCR0 | EQU       | 10E0H                  |   |                                           |

|--------|-----------|------------------------|---|-------------------------------------------|

| SYSCR1 | EQU       | 10E1H                  |   |                                           |

| SYSCR2 | EQU       | 10E2H                  |   |                                           |

|        | LD        | (SYSCR2), 0X11 B       | ; | Sets warm-up time to 2 <sup>16</sup> /fs. |

|        | SET       | 6, (SYSCR0)            | ; | Enables low-frequency oscillation.        |

|        | SET       | 2, (SYSCR0)            | ; | Clears and starts warm-up timer.          |

| WUP:   | BIT<br>JR | 2, (SYSCR0)<br>NZ, WUP | ; | Detects stopping of warm-up timer.        |

|        | SET       | 3, (SYSCR1)            | ; | Changes f <sub>SYS</sub> from fc to fs.   |

|        | RES       | 7, (SYSCR0)            | ; | Disables high-frequency oscillation.      |

| V D "  |           |                        |   |                                           |

Example 2: Setting the clock

Changing from low frequency (fs) to high frequency (fc).

| SYSCR0 | EQU     | 10E0H            |       |                                          |

|--------|---------|------------------|-------|------------------------------------------|

| SYSCR1 | EQU     | 10E1H            |       |                                          |

| SYSCR2 | EQU     | 10E2H            |       |                                          |

|        | LD      | (SYSCR2), 0X10 B | ; S   | ets warm-up time to 2 <sup>14</sup> /fc. |

|        | SET     | 7, (SYSCR0)      | ; E   | nables high-frequency oscillation.       |

|        | SET     | 2, (SYSCR0)      | ; C   | lears and starts warm-up timer.          |

| WUP:   | BIT     | 2, (SYSCR0)      | ; ] , | etects stopping of warm-up timer.        |

|        | JR      | NZ, WUP          | ;     | retects stopping or warm-up timer.       |

|        | RES     | 3, (SYSCR1)      | ; C   | hanges f <sub>SYS</sub> from fs to fc.   |

|        | RES     | 6, (SYSCR0)      | ; D   | isables low-frequency oscillation.       |

| V D "  | . N.I I |                  |       |                                          |

X: Don't care, -: No change

**TOSHIBA**

#### (2) Clock gear controller

ffph is set according to the contents of the clock gear select register SYSCR1<GEAR2:0> to either fc, fc/2, fc/4, fc/8 or fc/16. Using the clock gear to select a lower value of ffph reduces power consumption.

#### Example 3:

```

Changing to a high-frequency gear

SYSCR1 EQU 10E1H

```

LD (SYSCR1), XXXX0000B ; Changes f<sub>SYS</sub> to fc/2.

X: Don't care

#### (High-speed clock gear changing)

To change the clock gear, write the register value to the SYSCR1<GEAR2:0> register. It is necessary the warm-up time until changing after writing the register value.

There is the possibility that the instruction next to the clock gear changing instruction is executed by the clock gear before changing. To execute the instruction next to the clock gear switching instruction by the clock gear after changing, input the dummy instruction as follows (Instruction to execute the write cycle).

# (Example) SYSCR1

```

EQU 10E1H

```

Instruction to be executed after clock gear has changed

2007-02-16

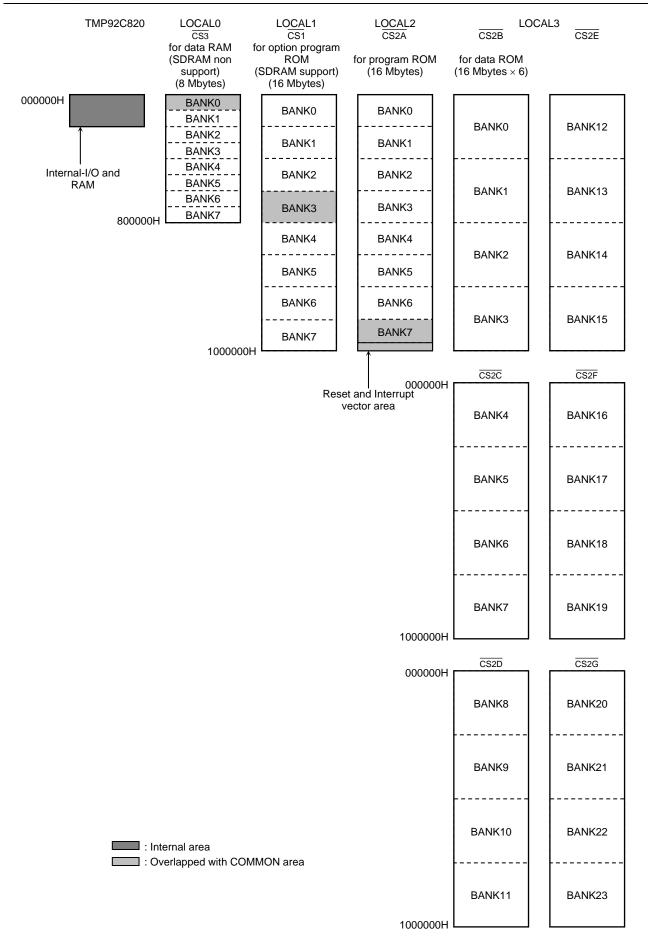

#### 3.3.4 Noise Reduction Circuits

Noise reduction circuits are built in, allowing implementation of the following features.

- (1) Reduced drivability for high-frequency oscillator

- (2) Reduced drivability for low-frequency oscillator

- (3) Single drive for high-frequency oscillator

- (4) Runaway provision with SFR protection register

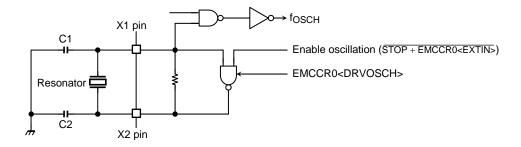

- (1) Reduced drivability for high-frequency oscillator

(Purpose)

Reduces noise and power for oscillator when a resonator is used.

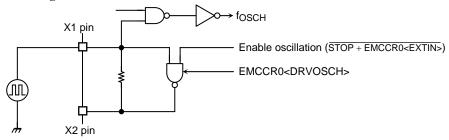

(Block diagram)

(Setting method)

The drivability of the oscillator is reduced by writing "0" to EMCCR0<DRVOSCH> register. By reset, <DRVOSCH> is initialized to "1" and the oscillator starts oscillation by normal drive ability when the power supply is on.

Note: This function (EMCCR0<DRVOSCH> = "0") is available to use in case of when  $f_{OSCH} = 6$  to 10 MHz condition.

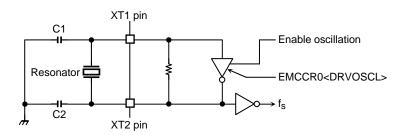

#### (2) Reduced drivability for low-frequency oscillator

#### (Purpose)

Reduces noise and power for oscillator when a resonator is used.

#### (Block diagram)

#### (Setting method)

The drivability of the oscillator is reduced by writing 0 to the EMCCR0<DRVOSCL> register. By reset, <DRVOSCL> is initialized to "1".

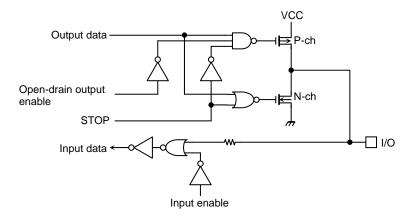

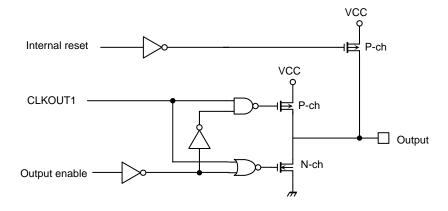

#### (3) Single drive for high-frequency oscillator

#### (Purpose)

Not need twin-drive and protect mistake operation by inputted noise to X2 pin when the external oscillator is used.

#### (Block diagram)

#### (Setting method)

The oscillator is disabled and starts operation as buffer by writing "1" to EMCCR0<EXTIN> register. X2 pin is always outputted "1".

By reset, <EXTIN> is initialized to "0".

#### (4) Runaway provision with SFR protection register

#### (Purpose)

Provision in runaway of program by noise mixing.

Write operation to specified SFR is prohibited so that provision program in runaway prevents that it is it in the state which is fetch impossibility by stopping of clock, memory control register (Memory controller, MMU) is changed.

And error handling in runaway becomes easy by INTP0 interruption.

#### Specified SFR list

- 1. Memory controller B0CSL/H, B1CSL/H, B2CSL/H, B3CSL/H, BECSL/H MSAR0, MSAR1, MSAR2, MSAR3, MAMR0, MAMR1, MAMR2, MAMR3, PMEMCR

- 2. MMU LOCAL 0/1/2/3

- 3. Clock gear SYSCR0, SYSCR1, SYSCR2, EMCCR0

#### (Operation explanation)

Execute and release of protection (Write operation to specified SFR) become possible by setting up a double key to EMCCR1 and EMCCR2 register.

## (Double key)

1st-key: Succession writes in 5AH at EMCCR1 and A5H at EMCCR2 2nd-key: Succession writes in A5H at EMCCR1 and 5AH at EMCCR2 A state of protection can be confirmed by reading EMCCR0<PROTECT>.

By reset, protection becomes OFF.

And INTPO interruption occurs when write operation to specified SFR was executed with protection on state.

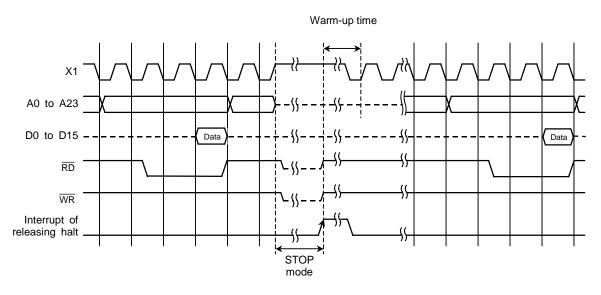

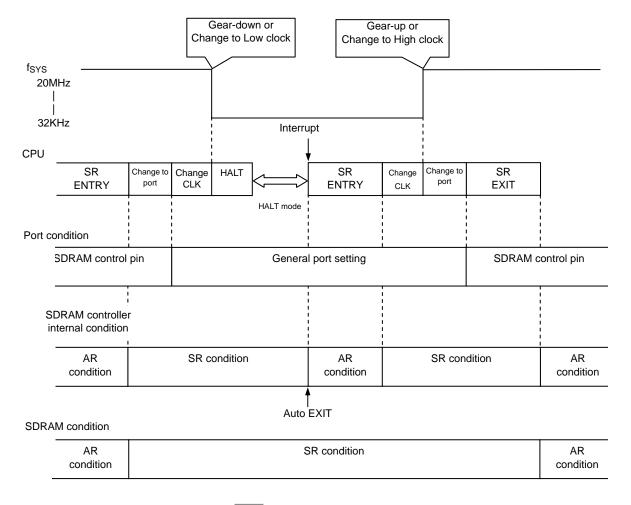

## 3.3.5 Standby Controller

#### (1) HALT modes

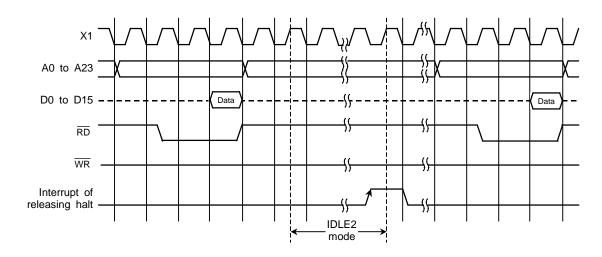

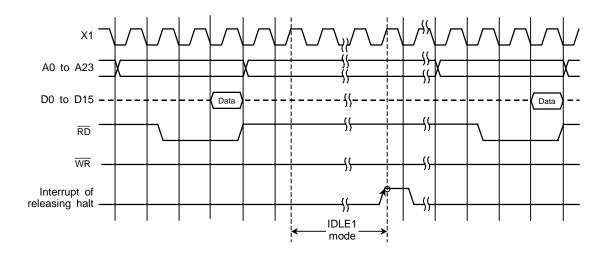

When the HALT instruction is executed, the operating mode switches to IDLE2, IDLE1 or STOP mode, depending on the contents of the SYSCR2<HALTM1:0> register.

The subsequent actions performed in each mode are as follows:

1. IDLE2: Only the CPU halts.

The internal I/O is available to select operation during IDLE2 mode by setting the following register.

Table 3.3.2 shows the registers of setting operation during IDLE2 mode.

| able 3.3.2 SFR Setting Operation during IDLE2 |                           |  |  |  |  |  |

|-----------------------------------------------|---------------------------|--|--|--|--|--|

| Internal I/O                                  | SFR                       |  |  |  |  |  |

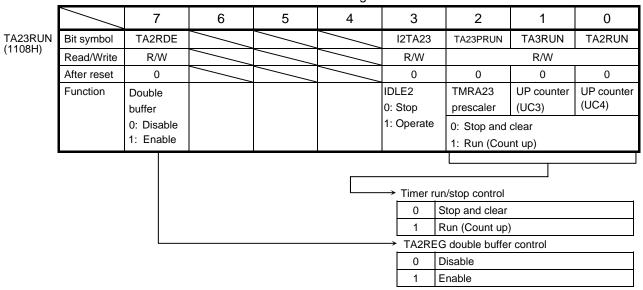

| TMRA01                                        | TA01RUN <i2ta01></i2ta01> |  |  |  |  |  |

| TMRA23                                        | TA23RUN <i2ta23></i2ta23> |  |  |  |  |  |

| TMRB0                                         | TB0RUN <i2tb0></i2tb0>    |  |  |  |  |  |

| SIO0                                          | SC0MOD1 <i2s0></i2s0>     |  |  |  |  |  |

| SIO1                                          | SC1MOD1 <i2s1></i2s1>     |  |  |  |  |  |

| AD converter                                  | ADMOD1 <i2ad></i2ad>      |  |  |  |  |  |

| WDT                                           | WDMOD <i2wdt></i2wdt>     |  |  |  |  |  |

| SBI                                           | SBIOBRO-I2SBIO>           |  |  |  |  |  |

Table 3.3.2 SFR Setting Operation during IDLE2 Mode

- 2. IDLE1: Only the oscillator, the RTC (Real time clock) and MLD (Melody-alarm generator) continue to operate.

- 3. STOP: All internal circuits stop operating.

The operation of each of the different HALT modes is described in Table 3.3.3.

|                 |                              | 1 0                                                    |                              |                |  |

|-----------------|------------------------------|--------------------------------------------------------|------------------------------|----------------|--|

|                 | HALT Modes                   | IDLE2                                                  | IDLE1                        | STOP           |  |

|                 | SYSCR2 <haltm1:0></haltm1:0> | 11                                                     | 10                           | 01             |  |

|                 | CPU                          |                                                        | Stop                         |                |  |

|                 | I/O ports                    | Keep the state when the HALT instruction was executed. | See Table 3.3.6, Table 3.3.8 | able 3.3.7 and |  |

|                 | TMRA, TMRB                   | Available to select                                    |                              |                |  |

| SIO, SBI (Note) |                              | operation block (Note)                                 |                              |                |  |

| Block           | AD converter                 |                                                        | St                           | on             |  |

|                 | WDT                          |                                                        | 31                           | ор             |  |

|                 | LCDC, SDRAMC                 |                                                        |                              |                |  |

|                 | interrupt controller         | Operate                                                |                              |                |  |

|                 | RTC, MLD                     |                                                        | Operate                      |                |  |

Table 3.3.3 I/O Operation during HALT Modes

Note: Prohibited in the synchronous mode of SBI circuit.

#### (2) How to release the HALT mode

These halt states can be released by resetting or requesting an interrupt. The halt release sources are determined by the combination between the states of interrupt mask register <IFF2:0> and the HALT modes. The details for releasing the halt status are shown in Table 3.3.4.

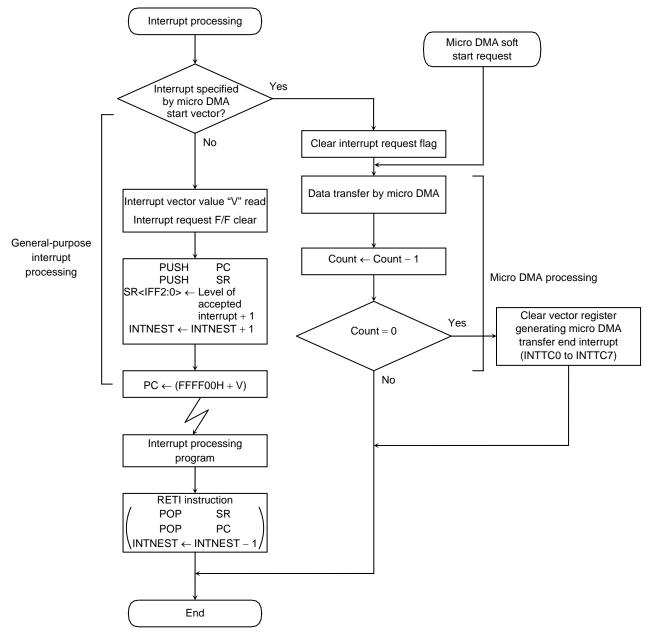

#### 1. Released by requesting an interrupt

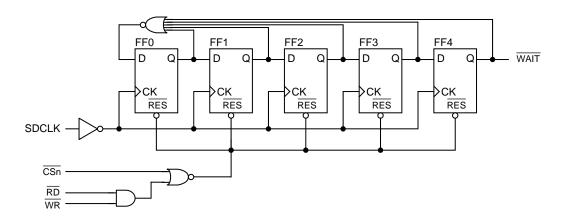

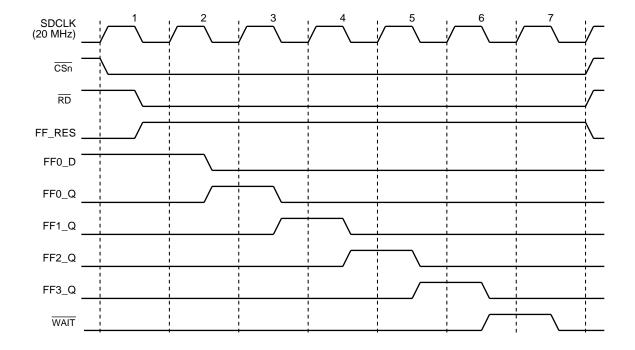

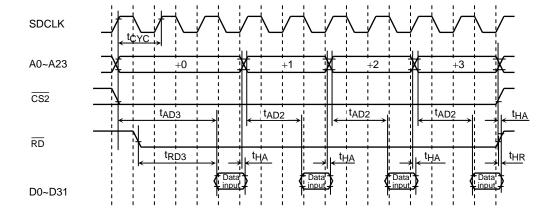

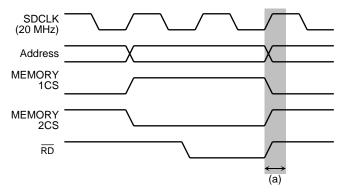

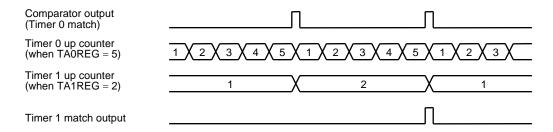

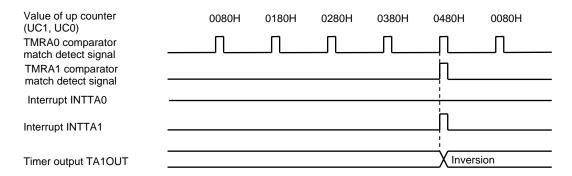

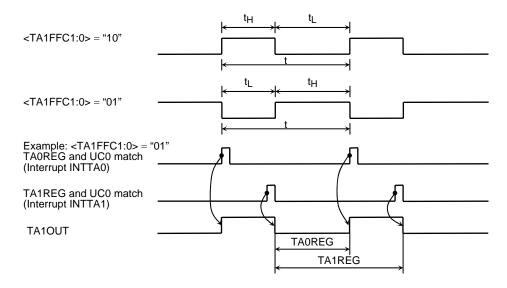

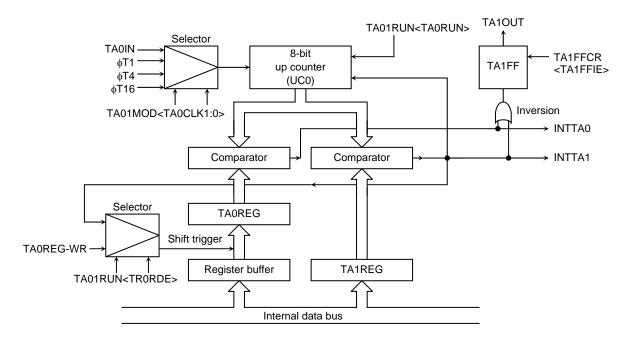

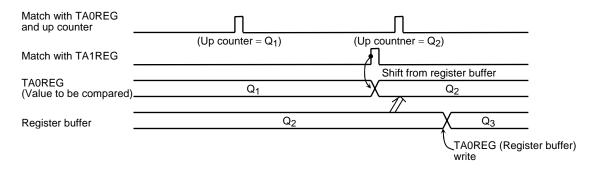

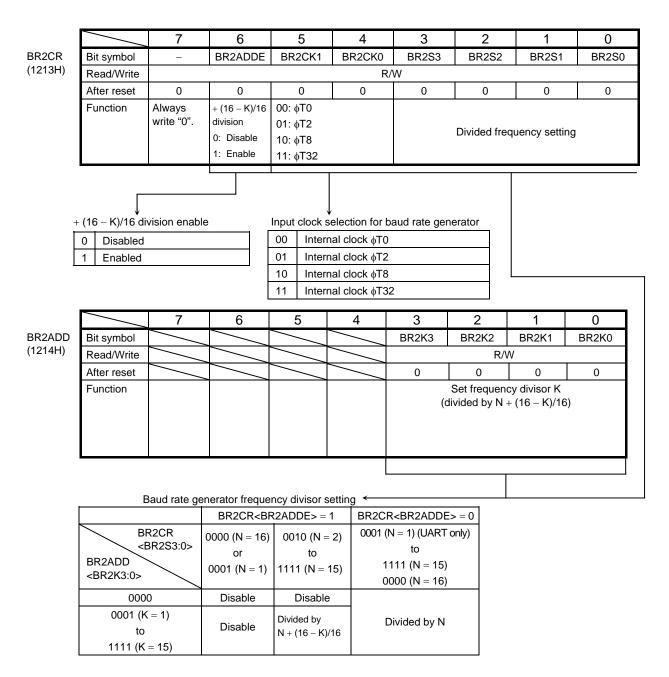

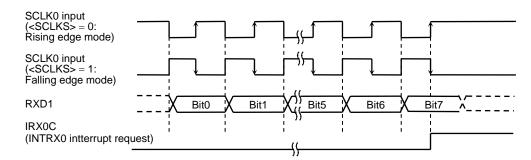

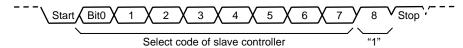

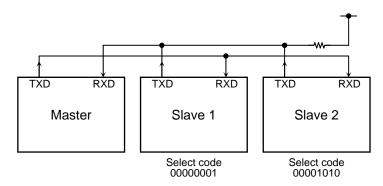

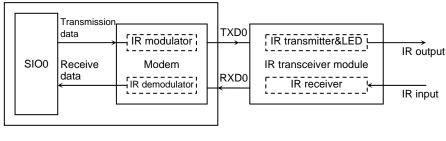

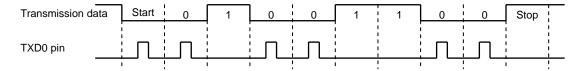

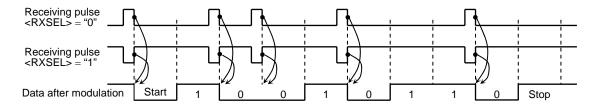

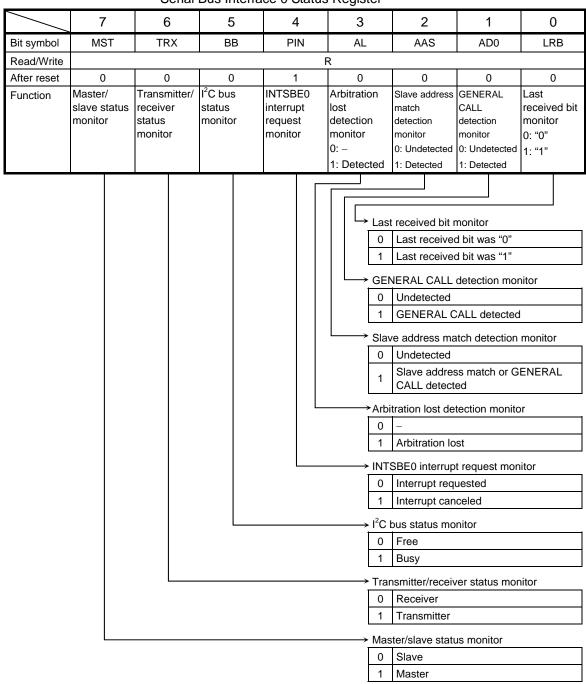

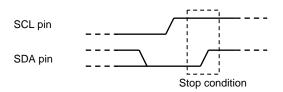

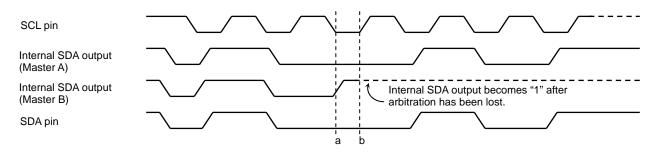

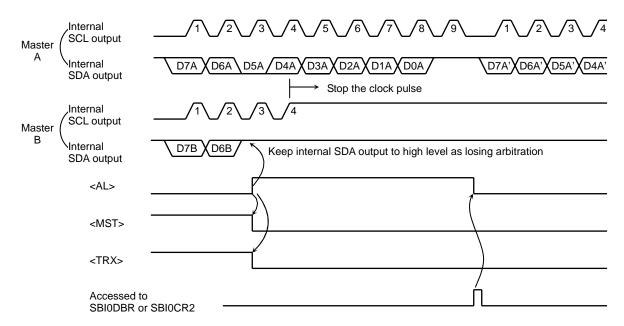

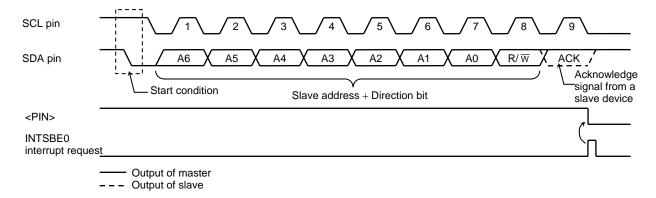

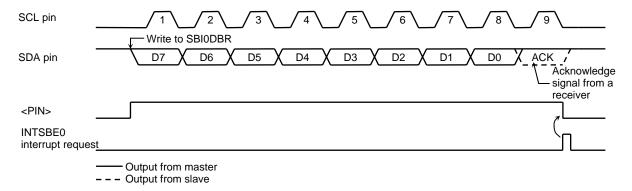

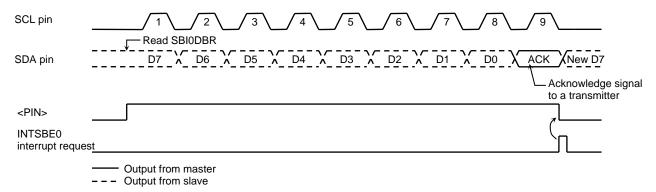

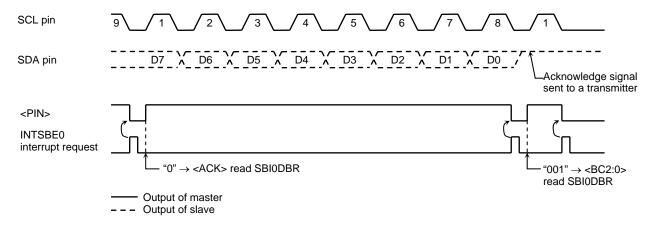

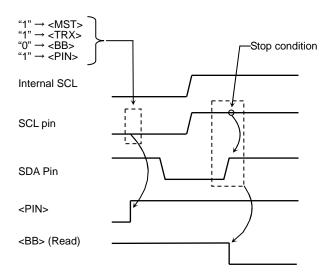

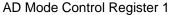

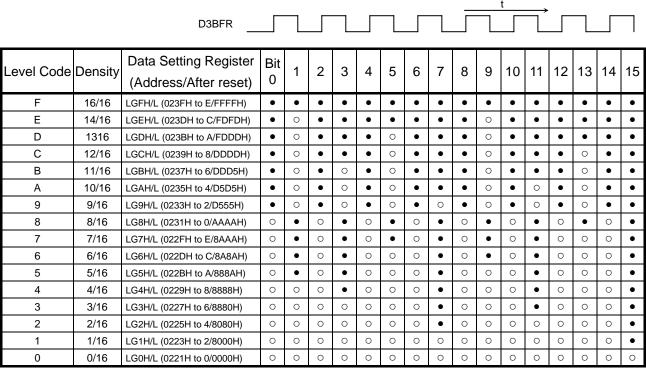

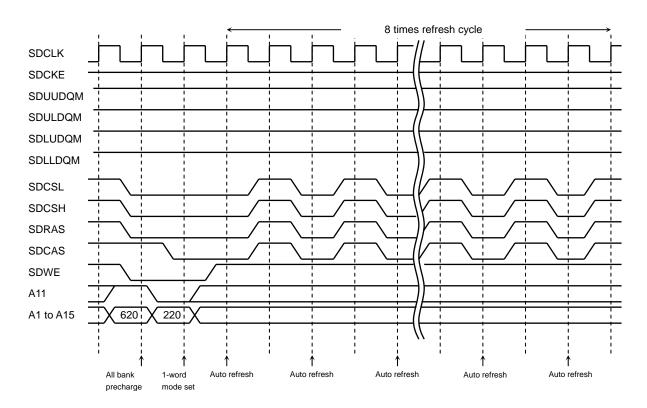

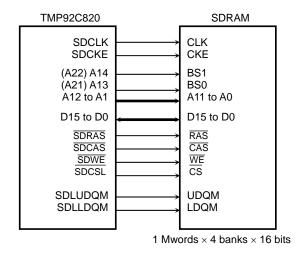

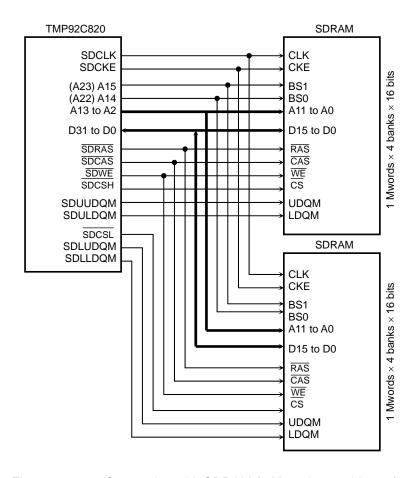

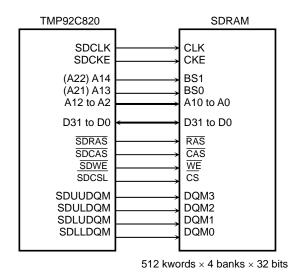

The operating released from the HALT mode depends on the interrupt enabled status. When the interrupt request level set before executing the HALT instruction exceeds the value of interrupt mask register, the interrupt due to the source is processed after releasing the HALT mode, and CPU status executing an instruction that follows the HALT instruction. When the interrupt request level set before executing the HALT instruction is less than the value of the interrupt mask register, releasing the HALT mode is not executed. (In non-maskable interrupts, interrupt processing is processed after releasing the HALT mode regardless of the value of the mask register.)